# Silicon Explorer II User's Guide

NOTE: Links and cross-references in this PDF file may point to external files and generate an error when clicked.

View the online help included with software to enable all linked content.

# **Table of Contents**

| Getting Started                      | 5  |

|--------------------------------------|----|

| About Silicon Explorer (SE)          |    |

| Connecting to the PC                 | 6  |

| Orange tion Oiling a Frankson        | _  |

| Connecting Silicon Explorer          |    |

| Powering Silicon Explorer II         |    |

| Connector Types                      |    |

| Silicon Explorer Target Connections  |    |

| Silicon Explorer PC Connection       |    |

| Device Settings                      |    |

| Act1 and A40MX Connection            |    |

| Act2/XL/Act3/DX/A42MX Connections    |    |

| SX/SX-A/eX/RTSX/RTSX-S Connections   |    |

| Axcelerator Connection               |    |

| External Logic Analyzer Pinout Table |    |

| Using the Software                   | 18 |

| Software Settings                    |    |

| Silicon Explorer Software            |    |

| Using the Command Mode               |    |

| Using the Analyze Module             |    |

| •                                    |    |

| Main GUI                             |    |

| Silicon Explorer Tool Bar            |    |

| Main Window                          |    |

| Shortcuts                            |    |

| Data Display                         | 27 |

| Bussed Signals                       |    |

| -                                    |    |

| Rearrange Channels Pattern           |    |

| Find                                 |    |

| Highlight                            | 31 |

| Data Files                           |    |

| Copy Display Data                    |    |

| Readback Data                        |    |

| Troubant Balannin                    |    |

| Logic Analyzer Concepts              | 33 |

| Asynchronous Sampling                | 35 |

| Understanding Triggering             | 37 |

| Trigger                              | 37 |

| Auto-Trigger                         | 37 |

|                                      |    |

### Table of Contents

| Triggering Silicon Explorer                               | 38 |

|-----------------------------------------------------------|----|

| Analyzer Controls                                         | 40 |

| Probe Instrument                                          |    |

| Run Controls                                              | 42 |

| Sampling                                                  |    |

| Troubleshooting Silicon Explorer                          | 43 |

| Troubleshooting Errors                                    |    |

| Troubleshooting General                                   |    |

| Troubleshooting Software                                  |    |

| Troubleshooting Hardware                                  |    |

| •                                                         |    |

| Debugging AX/eX/SX/SX-A Devices Using Silicon Explorer II |    |

| Internal Probing Feature for Antifuse Families            | 51 |

| SDO Pin Locations                                         | 53 |

| ACT2 and 1200XL Families                                  | 53 |

| ACT3 Family SDO Pin Locations                             | 54 |

| A3200 Family SDO Pin Locations                            | 55 |

| A42MX SDO Pin Locations                                   | 56 |

| RT SDO Pin Locations                                      | 57 |

| Specifications                                            | 59 |

| Silicon Explorer Specifications                           |    |

|                                                           |    |

| Accessories                                               | 60 |

| Glossary of Terms                                         | 62 |

| Product Support                                           | CE |

| Product Support                                           |    |

| Contacting the Customer Technical Support Center          |    |

|                                                           |    |

# **Getting Started**

# About Silicon Explorer (SE)

The Silicon Explorer<sup>™</sup> Logic Analysis software is designed to support logic instruments such as a timing analyzer, a state analyzer, and a probe pilot. Each of these instruments provides specific capabilities for acquiring and or viewing data.

Microsemi has previously offered Silicon Explorer (SE) II Lite, SE Lite and SE I (all now discontinued).

SE full-version has a built in logic analyzer functionality. SE has a 22-pin (18 channels, a clock, VCC, GND, and clock GND) and a 16-pin connector for controlling the Action Probe circuitry and reading the design checksum. It also has a 26-pin connector for programming ProASIC devices. The Silicon Explorer II logic-analysis system is enhanced to support an external power supply, which permits internal probing of 5.0V, 3.3V, and 2.5V FPGAs. Other features include four-levels of triggering, decompression on download to speed up response time and system acquisition rates up to 100MHz.

Silicon Explorer II enables control of the Action Probe circuitry, a patented architectural feature built into all of Actel's antifuse devices that allows access to any internal node from selected external pins. SE II integrates two diagnostic tools, the Command module and the Analyze module, into a single diagnostic and logic analysis device that attaches to a PC's standard COM port. The Command module of the Explore software lists all the observable nets in the FPGA. Select the desired net in the list and click the PRA or PRB button to display the signal on the Analyze module. The Command module also reads back the design's checksum. Also, it is possible to read back the CHECKSUM of a device after it has been secured. You can use the design's checksum to verify that you programmed the correct design in the FPGA. The Analyze module is an 18-channel logic analyzer that automatically displays the signals for both probe outputs (and up to 16 additional signals) on the target system. You may sample data asynchronously at 66 MHz. Channel 1 and 2 of the logic analyzer connect to the PRA and PRB signals on the FPGA automatically. Silicon Explorer II uses the remaining 16 channels of the logic analyzer to examine other signals on the board. Silicon Explorer has no memory devices. File data cannot be stored on any of the non-volatile memory

### **Device Support**

Silicon Explorer supports all antifuse devices.

### **System Requirements**

components.

The system requirements for Silicon Explorer II are:

- Designer R1-2000 or later

- Pentium-133 or equivalent

- Microsoft® Windows 98 or NT™ 4.0 SP6, 2000, XP

- 8 MB RAM (minimum); 16 MB recommended

### Kit Contents

The Silicon Explorer kit contains the following:

Table 1 · Silicon Explorer Kit Contents

| Hardware/Software             | Part Number         |

|-------------------------------|---------------------|

| Silicon Explorer II           | SILICON-EXPLORER II |

| Silicon Explorer User's Guide | 5029134             |

| Hardware/Software                       | Part Number              |

|-----------------------------------------|--------------------------|

| Ribbon Cable Assembly                   | RIBBON & BREAKOUT CABLES |

| Quick Pro Clips                         | 1630073                  |

| Accessory Bag                           | 1630078                  |

| Power Supply                            | SE II PWR SUPPLY         |

| Flying Lead Cable Assembly              | SI-EX-TCA                |

| CD Containing Silicon Explorer Software | LIB-CD-PACK-PC           |

# Connecting to the PC

Silicon Explorer II connects to a standard serial port using an 8250 or 16550 UART. Establish communication via the 9-Pin D-Sub connector.

# **Connecting Silicon Explorer**

# Powering Silicon Explorer II

SE II draws power from the external power supply (provided) or by connecting the VIO pin to a power source (such as might exist on a PCB). You must connect VIO to a reference voltage when using the external power supply. Microsemi recommends using the external power supply when the target system cannot supply enough current to run SE II. The table below lists possible power configurations.

Table 2 · Power Configurations for Silicon Explorer II

| I/O Power Supply | External SE II Power Supply | VIO  |

|------------------|-----------------------------|------|

| 2.5V             | Required                    | 2.5V |

| 3.3V             | Optional (see note)         | 3.3V |

| 5.0V             | Optional                    | 5.0V |

Note: Note: If your current system is limited, you must use the external power supply and use VIO as the reference voltage.

When you apply power, the yellow "heartbeat" LED on Silicon Explorer II begins to blink. Microsemi designed Silicon Explorer II hardware to withstand abuse normally found in a lab environment. However, long term exposure to out-of-range conditions can cause failure. In particular, long term connection to reverse- or over-voltage power conditions can cause thermal failure.

### **Current Consumption**

Silicon Explorer II is a CMOS device and exhibits very low current consumption when idle. Current consumption rises rapidly to several hundred milliamps during acquisition. If your power supply is unable to supply the necessary current, SE II or your target may reset. The table below is a guide to typical current consumption based on an acquisition rate at 5V — current will be proportionately higher at 3V.

Table 3 · Typical Current Consumption

| Acquisition Rate | Current@5V |

|------------------|------------|

| IDLE             | 75 mA      |

| 10 MHZ           | 300 mA     |

| 20 MHz           | 400 mA     |

| 50 MHz           | 500 mA     |

| 100 MHz          | 700 mA     |

# **Connector Types**

Silicon Explorer II has a 22-pin (18 channels, a clock, VIO, GND, and clock GND), a 26-pin, and a 16-pin connector for controlling the Action Probe circuitry and reading the design checksum.

Table 4 · Connector Types

| Connector Type | Mode                 |

|----------------|----------------------|

| 22-pin         | Logic Analysis       |

| 16-pin         | Action Probe Control |

| 26-pin         | Not Used             |

The pins are assigned according to the table below.

| Source | Pin       |

|--------|-----------|

| PRC    | Pin 6     |

| PRD    | Pin 7     |

| GND    | Pin 1, 21 |

| VIO    | Pin 2     |

### **Logic Analysis**

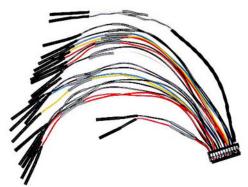

Microsemi Silicon Explorer II ships with a replaceable target cable assembly (SI-EX-TCA) that interfaces Silicon Explorer II with your target system. To connect Silicon Explorer II, align the short red wire on the SI-EX-TCA with no dot on the case and fully insert the 2 mm header (Digi-Key MHD16K-ND). The contacts on the SI-EX-TCA accept standard 0.025" round or square test accessories.

Connect any of Silicon Explorer IIs 18-channel leads to the desired target signals using standard test accessories.

The Silicon Explorer units come with cables that are terminated with a connector so you can insert a post on the board. A bag of clips that attach to these connectors to clip onto a post or pin of the device, or another cable is also included.

### **Probe Leads**

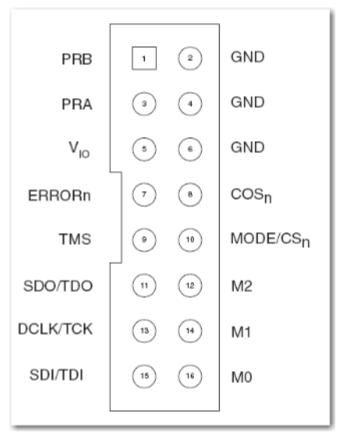

Connect the probe leads by attaching one of two supplied cable assemblies. One 16-pin cable assembly terminates in individual 0.025 connectors that connect to 0.025 headers or microclips according to the labels on the wires. The other assembly interfaces directly to the target board with a 16-pin header when you install the target according to the pin-out shown in the figure and listed in the table below.

Figure 1 · Silicon Explorer II Probe Connector Pin-Out

Table 5 · Matching Probe Pins to Device Pins <sup>1</sup>

| Probe            | ACT1,40MX        | ACT2, 42MX, 3200DX | SX/SX-A/eX       |

|------------------|------------------|--------------------|------------------|

| Mode             | Mode             | Mode               | Not Used         |

| GND <sup>2</sup> | GND              | GND                | GND              |

| SDI/TDI          | SDI              | SDI                | TDO              |

| DCLK/TCK         | DCLK             | DCLK               | тск              |

| SDO/TDO          | PRA              | SDO                | TDO              |

| TMS              | Not Used         | Not Used           | TMS              |

| V <sub>IO</sub>  | V <sub>CCI</sub> | V <sub>CCI</sub>   | V <sub>CCI</sub> |

| PRA              | PRA              | PRA                | PRA              |

| PRB              | PRB              | PRB                | PRB              |

| Ch3 <sup>3</sup> | -                | -                  | PRC              |

| Ch4 <sup>3</sup> | -                | -                  | PRD              |

<sup>&</sup>lt;sup>1</sup> ERRORn, CONn, M2, M1, M0 pins are not required for use with Silicon Explorer II.

<sup>&</sup>lt;sup>2</sup> You can connect any or all GND pins. For best results, connect all GND pins.

Note: Note: Chan 16/QO, Chan 17/Q2, and Chan 0/CH0/TRIG refers to a feature in a previous product and is not available in Silicon Explorer.

# Silicon Explorer Target Connections

### **Signal Connections**

Silicon Explorer includes a replaceable <u>TCA</u> cable which interfaces to your target system. The TCA contains flying leads for input signals, clock, power and ground. Each wire is identified by a printed label.

### To connect Silicon Explorer to the target signals:

- 1. Insert the TCA 2 mm header into Silicon Explorer. The connector is keyed and will only go in one way.

- Connect the leads to the circuit under test using the .025" contacts, or test accessories such as probe clips, or clip-over adapters.

### To avoid difficulty:

- Be sure the TCA is firmly seated in the mating connector.

- Remember that the ground lead is also the signal return. Make a good connection directly to the

ground plane or a ground point near the highest frequency signal that you will be acquiring. If possible

connect all of the ground leads to the target board for best signal quality.

### **External Clock**

Synchronous acquisitions are made by connecting the Clock input leads of the target cable assembly (TCA) to the clock signal on the circuit under test. Silicon Explorer is specified to sample using an external clock to 66 MHz.

#### To connect to an external clock:

- 1. Insert the TCA 2 mm header into Silicon Explorer. The connector is keyed and will only go in one way.

- Connect the external clock input lead of the target cable assembly, labeled CKLIN, to the clock signal on the target board.

- Connect the clock ground wire to the ground plane or a ground point physically close to the clock signal.

### To avoid difficulty:

- The clock ground wire should be connected for best signal integrity.

- Be sure the TCA is firmly seated in the Silicon Explorer mating connector.

### See Also

### Sampling

**Understanding Synchronous Sampling**

### **Power**

Silicon Explorer is powered by +3V to +5V, which is supplied by the target board, the supplied power adapter (Silicon Explorer II only), or an external power supply. To determine if a power adapter or external supply is needed, see the current consumption section.

Caution: Although Silicon Explorer is designed to withstand the abuse normally found in a lab environment, long term exposure to out of range conditions can cause failure. In particular long term connection to reverse or over-voltage power conditions can cause thermal failure.

<sup>&</sup>lt;sup>3</sup> These are used with AX/RTAXS devices.

### **Target Power**

Power and ground leads are provided on the target cable assembly (TCA) for connection to a +3V to +5V source. Two micro-grabber test clips are used for connection to power test points on the target board.

- 1. Insert the target cable assembly (TCA) 2 mm header into Silicon Explorer. The connector is keyed and will only go in one way.

- 2. With power removed from the target circuit, connect the TCA power and ground leads to the power (+3V to +5V) and ground test points on the target board. The TCA power lead is labeled +5V but can be connected to any voltage between +3V and +5V on the target.

- 3. Apply power to the target circuit.

Note: Note: The amount of current drawn by Silicon Explorer depends on the sample rate selected and number of active input channels and ranges from 125mA to 750mA with a 5V supply.

### **Power Adapter**

The supplied power adapter (Silicon Explorer II) is a compact switching power supply that provides +5V at 1 A for applications where target power is not available or insufficient. The power supply is plugged into the power jack located on the Silicon Explorer II next to the serial cable.

- 1. With the power adaptor disconnected from any wall outlet, insert the power adaptor's plug into the power jack on the Silicon Explorer II.

- 2. Connect the Silicon Explorer II ground leads to the target.

- 3. Plug the power adaptor into a wall outlet.

### **External Power Supply**

An external +5V power supply may be used to power Silicon Explorer when target power in insufficient. Power and ground leads are provided on the target cable assembly (TCA) for connection to the +5V source. Two micro-grabber test clips can be used for connection to ground test points on the target board.

- 1. Insert the target cable assembly (TCA) 2mm header into Silicon Explorer. The connector is keyed and will only go in one way.

- 2. With the external power supply turned off, connect the Silicon Explorer and external power supply ground leads to the ground plane of the circuit under test.

- 3. Connect the Silicon Explorer and external power supply +5V leads together.

- 4. Switch on the external supply.

### **Current Consumption**

Silicon Explorer is a CMOS device and exhibits very low current consumption at idle, rising rapidly to several hundred milliamps during acquisition. The amount of current required depends on the sample rate and number of active channels. If your power supply is unable to supply the inrush current, Silicon Explorer or your target may reset. The following lists the minimum and maximum current requirements at 5V. Current will be proportionately higher at 3V:

| Idle                | 125 mA |

|---------------------|--------|

| Minimum Acquisition | 350 mA |

| Maximum Acquisition | 750 mA |

### **Debug Port**

You can connect the probe leads by attaching one of two supplied cable assemblies. One cable assembly terminates in individual 0.025 receptacles that can connect to 0.025 headers or micro-clips according to the labels on the wires - the other assembly interfaces directly to the target board when a 16-pin header is installed on the target according to the pin-out shown on the bottom of the Silicon Explorer.

The Probe A and B pins on the probe connector may be selected as the source for logic analyzer channels 1 and 2 respectively, by clicking on the # field in the Waveform window and selecting PRA or PRB as the source. Selecting the probe pins as the source disables the CH1 and/or CH2 inputs from the target cable assembly.

### See Also

• <u>Probing</u>

# Silicon Explorer PC Connection

<u>Device Settings</u> Hardware Connection

### See Also

Target Connections

Troubleshooting

# **Connecting Silicon Explorer**

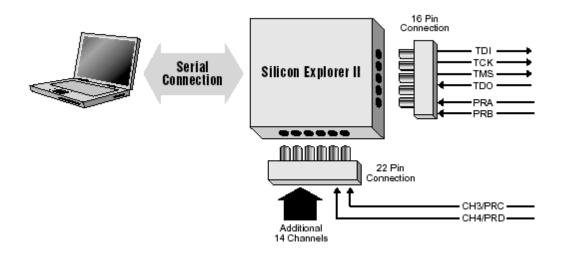

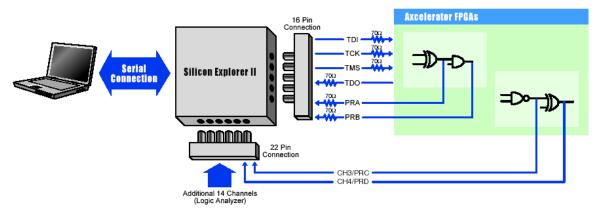

The Silicon Explorer POD is connected to your PC with a 9 pin Serial Port cable that is permanently attached to the POD. The Silicon Explorer POD is connected to the target by two cables. The first cable is a 16 pin ribbon cable that contains the control signals for addressing the PRA, PRB, PRC\*, and PRD\* Action Probes (tm) within the Microsemi FPGAs. The second cable is a 22 pin flying-lead cable for connecting the logic analyzer channels to the target and optionally an external clock. (\*Action Probes (tm) PRC and PRD are only available for Axcelerator devices and need be connected to the Channel 3 and Channel 4 leads by the user.)

Figure 2 · Connecting Explorer POD to PC

Note: Note: The Silicon Explorer units come with cables that are terminated with a connector into which a post on the board can be inserted. Clips which can be attached to these connectors and used to clip onto a post or pin of the device, or another cable are also included.

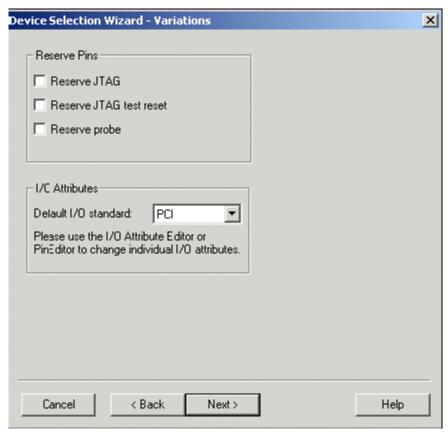

# **Device Settings**

The Silicon Explorer connects to a standard RS-232 serial port using either an 8250 or 16550 UART. Although 16550 UARTs are not required for hi-speed operations some serial ports do not use driver/receivers that are rated for the full 115,200 baud data rate used by the Pod and may not work with extension cables.

To attach Silicon Explorer to your PC, connect the Silicon Explorer 9-Pin D-Sub connector to a serial port (COM 1 through 4) on your PC

Note: Note: If you wish to use a serial extension cable with your Silicon Explorer choose a shielded cable of good quality. RTS and CTS are required as well as Transmit, Receive, and Ground. DSR is connected to DTR but is not required for operation.

You can select a serial port (COM1 through 4) from the menu bar. The Silicon Explorer application polls the Silicon Explorer continuously for activity. Setting the port to Demo mode prevents the application from opening any COM ports on your system.

### To select the COM port:

On the Device menu, click Port, then click the appropriate COM port.

Select **Demo** to view data files without Silicon Explorer connected.

The Silicon Explorer software defaults to 115,200 baud at this speed data transfer will be less than 20 seconds for the entire buffer. On some slow systems (486-33 or less) particularly those with 8250 UARTs, better performance may occur at 57,600 baud due to the need to retry blocks at high speed.

### To change the baud rate:

On the Device menu, click **Baud.** Click the appropriate baud rate.

### **Verify Communication**

The Silicon Explorer software reports communication status on the status bar. When the Silicon Explorer has been properly connected, configured and powered, the status will show IDLE. If the status bar reports POLL or N/C (not connected) then the link has not been established. See the <u>troubleshooting</u> page for assistance.

### Act1 and A40MX Connection

The figure below shows the connection of Silicon Explorer II to the Act1 and A40MX families of devices. The Act1 and A40MX families of devices have two probe outputs, PRA & PRB, that connect to the Silicon Explorer's 16 pin connector.

# ACT1/A40MX Silicon Explorer Setup

Serial Connection to Windows PC

Silicon

Explorer

Silicon

PRB

PRA

ACT1/A40MX

ACT1/A40MX

Figure 3 · Silicon Explorer II Connection to Act1 and A40MX Devices

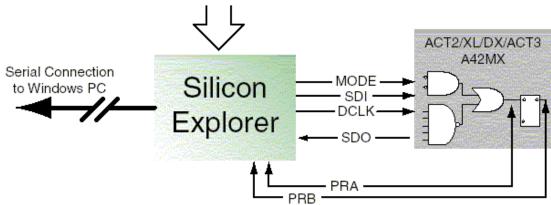

### Act2/XL/Act3/DX/A42MX Connections

The figure below shows the connection of Silicon Explorer II to the Act2, Act3, XL, DX, and A42MX families of devices. All of these families of devices have two probe outputs, PRA & PRB, that connect to the Silicon Explorer's 16 pin connector.

# ACT2/XL/ACT3/DX/A42MX Silicon Explorer Setup

16 Logic Analyzer Channels

Figure 4 · Silicon Explorer II connection to Act, XL, DX, and A42MX Devices Note: Note: Designer R398 or later is required for probe file creation.

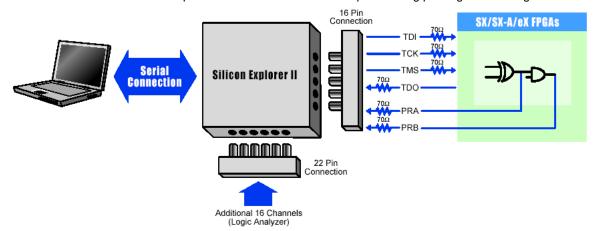

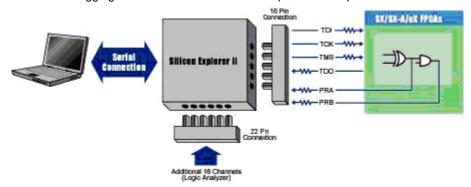

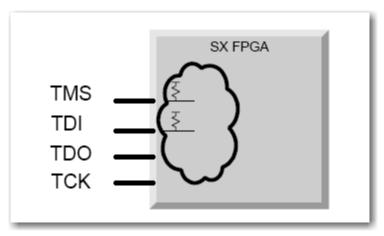

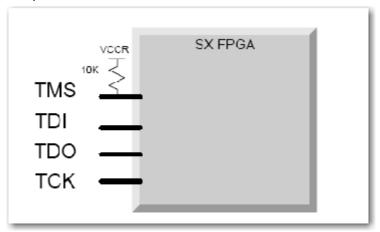

### SX/SX-A/eX/RTSX/RTSX-S Connections

The figure below shows the connection of Silicon Explorer II to the SX, SX-A, RTSX, RTSX-S, and eX families of devices. All of these families of devices have two probe outputs, PRA & PRB, that connect to the Silicon Explorer's 16 pin connector.

The probing of an SX-A, RTSX-S, or eX device may require special setup. Microsemi recommends that you use a series 70 ohm termination on all the probe connectors (TDI, TDO, TCK, TMS, PRA, PRB). The 70 ohm series termination prevents data transmission corruption during probing and reading checksum.

Figure 5 · Silicon Explorer Connection

Note: Note: Designer R398

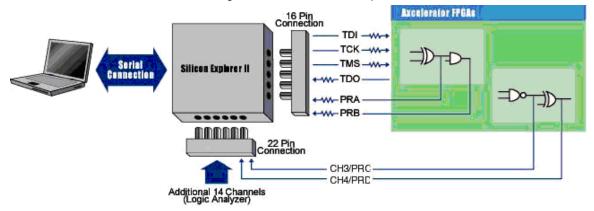

### **Axcelerator Connection**

The figure below shows the connection of Silicon Explorer II to the Axcelerator family of devices. The Axcelerator family of devices has four probe outputs unlike earlier device families. Each member of the

Axcelerator family has four external pads: PRA, PRB, PRC, and PRD. These can be used to bring out four probe signals from the Axcelerator device (note that the AX125 only has two probe signals that can be observed: PRA and PRB). Each core tile has up to two probe signals.

Shown in this figure are the 70 ohm series termination resistors needed on TDI, TCK, TMS, TDO, PRA and PRB. Probe outputs PRC and PRD do not need termination resistors on the board because resistors are built into the CH3 and CH4 leads. The 70 ohm series termination prevents data transmission corruption during probing and reading checksum.

Note: Note: Signals in Axcelerator devices can only be probed for speeds of 28 MHz or less.

Figure 6 · Silicon Explorer II Connection to Axcelerator Device

Note: Note: Designer R1-2003 SP3 or later is required for Axcelerator probe file creation.

# **External Logic Analyzer Pinout Table**

Table 6 · External Logic Analyzer Pinout Table

| Pin Number | Function |

|------------|----------|

| 1          | GND      |

| 2          | +V5      |

| 3          | CH0/TRIG |

| 4          | CH1      |

| 5          | CH2      |

| 6          | СНЗ      |

| 7          | CH4      |

| 8          | CH5      |

| 9          | CH6      |

| 10         | CH7      |

| 11         | CH8      |

| 12         | СН9      |

| 13         | CH10     |

| Pin Number | Function                         |

|------------|----------------------------------|

| 14         | CH11                             |

| 15         | CH12                             |

| 16         | CH13                             |

| 17         | CH14                             |

| 18         | CH15                             |

| 19         | CH16/Q0                          |

| 20         | CH17/Q1                          |

| 21         | GND (CLK ground)                 |

| 22         | CLKIN (for synchronous sampling) |

# **Using the Software**

# Software Settings

Silicon Explorer II sets itself to **Demo** mode on installation. From the Device menu, choose **Silicon Explorer** II or **Silicon Explorer**, depending on your version of the hardware.

Choose the desired port (COM1 through COM4) from the Port drop-down list in the **Device** menu. The software continuously polls the hardware for activity. Setting the port to the Demo mode prevents the application from opening any COM ports on your system. The serial port saves information in the analyze.ini file found in your Windows directory. The default data transfer speed is 115,200 baud. At this speed data transfer for the entire buffer is less than 15 seconds.

Note: Note: Many notebook computers share the external COM port with a built-in infrared (IR) port. You may have to enter your CMOS setup menu to enable the external COM port.

# Silicon Explorer Software

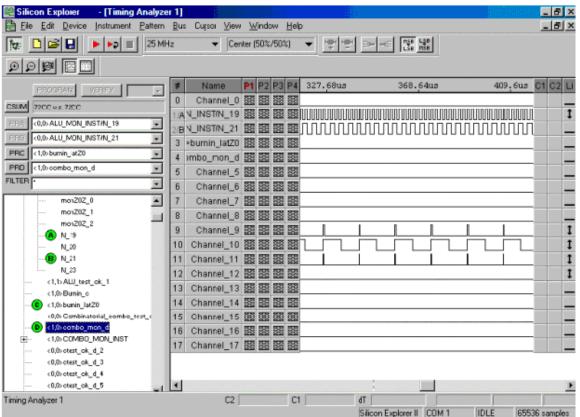

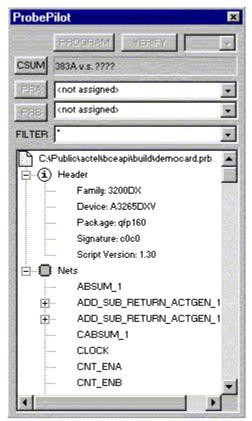

The Explorer software consists of two components, the Command module and the Analyze module. The Command module of the Explore software lists all the observable nets in the FPGA. Use the Command module to verify that you programmed the correct design in the FPGA. The Analyze module is an 18-channel logic analyzer that automatically displays the signals for both probe outputs (and up to 16 additional signals) on the target system. PRC and PRD are not displayed for other device families. The figure below shows the Silicon Explorer with an Axcelerator probe file loaded.

Figure 7 · Silicon Explorer Window with an AX Probe File

# Using the Command Mode

The **Command** module is the interface used to select internal nodes in the Microsemi FPGA family. The Command module lists all the observable nets in the FPGA. You can select the desired net in the list and click the PRA or PRB button to display the signal on the Analyze module. The Command module also reads back the design's checksum. You can still read back the CHECKSUM of a device after it has been secured and you can use the design's checksum to verify that you programmed the correct design in the FPGA.

Figure 8 · Command Module

### To open a probe file:

- 1. From the Start menu, choose **Programs > Designer > Silicon Explorer** to launch Silicon Explorer.

- From the File menu choose Open. Choose (\*.prb) as the File type and double-click the desired probe

file. You can also open a probe file in Silicon Explorer by double-clicking the Open Actel Probe File

icon.

Explore uses a PRB file exported from Designer during analysis. The exported file contains device information, net names, and node location information. After the PRB file opens, verify the information displayed in the tree structure in the Analyze window.

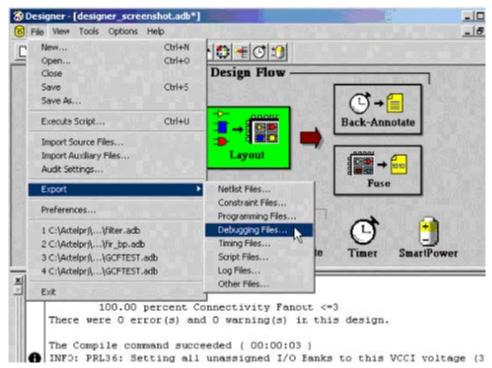

### To export a probe file from Designer:

- 1. Launch Designer.

- 2. Open your design file

- 3. Go to File > Export to view the Export dialog box.

Figure 9 · Opening the Export Debugging Dialog Box

- 4. Select Auxiliary File from the File Type pull-down menu.

- 5. Select **Probe** from the **Type** pull-down menu.

- 6. Select **OK** to continue and then save the Probe file.

You can also generate a AFM or probe file using the Generate Programming Files: Fuse Files dialog box. See the figure below. Note that the **Generate Probe File Also** box is checked.

Figure 10 · Generate Programming Files Dialog Box

### To verify checksum:

- 1. Make sure that the SDO/TDO is connected.

- Click the Checksum button.

- Once you open a Probe file and make a device connection, read the checksum of the target device and compare it to the checksum in the Probe file by double-clicking the Checksum button. The table below lists and explains the error messages.

Note: When reading an FPGA checksum with Silicon Explorer, the Acquire/AutoRun button and the Stop button may randomly toggle. If this happens, click the Acquire button and then the Stop button. This returns the software to normal state.

Table 7 · Checksum Error Messages

| Error Message             | Explanation                                                                                                                                                           |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Checksum:<br>383A vs ???? | Checksum is not readable because the probe is disconnected or not powered.                                                                                            |

| Checksum:<br>383A vs 0000 | Checksum does not match the file or The SDO/TDO probe-side pin is not properly connected to the device. Connector Types contains a listing of the proper connections. |

### To probe a node:

- 1. Select the designed signal from the tree by clicking the net name. Use the filter box to search nets quickly, and use the multiple wildcard characters ("\*") to restrict your search.

- 2. Click the PRA or PRB button. Silicon Explorer II routes the selected node to the probe pin and switches the corresponding analyzer input to the probe connector.

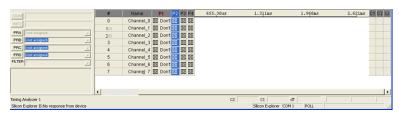

# Using the Analyze Module

### To use the Analyze Module:

Open Silicon Explorer II and check the status in the lower right corner of the display. If you have properly selected the COM port and powered up Silicon Explorer II, then the status is IDLE. The Analyze module captures 64K samples of each channel and uploads them to the host over the serial port.

Figure 11 · Analyze Module

2. Set acquisition parameters from the tool bar or the pull-down menus.

Figure 12 · Acquisition Parameters

| Acquisition<br>Speed | 10 Khz to 100 MHz asynchronous |

|----------------------|--------------------------------|

| Trigger              | 25%                            |

| Position             | 50%                            |

### **Product Support**

|                    | 75%                                                                                                                                                                        |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trigger<br>Pattern | Click on individual signals in the Px Column to specify don't care, low, high, rising, falling, or either edge. The rigger patterns is the logical AND of the 18 patterns. |

3. Once you set the acquisition parameters, click the Run button (red triangle) to begin acquisition. The analyzer begins capturing data until Silicon Explorer II recognizes the trigger pattern or you press the stop button (black square). During the capture period, the status window displays "PRE" for the pretrigger state (although you may not see it if the trigger pattern matches quickly).

Next, Silicon Explorer II enters the POST state and samples data after the trigger pattern (or stop button) until it fulfills the post trigger requirement. Then, it uploads the data to the host (READ State with progress indicator). The entire upload process takes less than 15 seconds, although you may zoom in and view data immediately because the buffer uploads as a background task.

# **Main GUI**

### Menu Bar

The Menu Bar provides pull-down menu access to all Silicon Explorer settings, controls and display functions.

Figure 13 · Menu Bar

Keyboard shortcuts are also indicated in the menu choice.

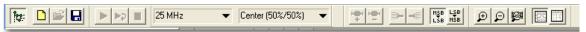

# Silicon Explorer Tool Bar

The Tools Bars contain button-style controls which are grouped together into individual tool bars. The grouped tool bars can be viewed, hidden or rearranged.

Figure 14 · Tool Bar

Table 8 · Tool Bar Icons and Description

| Icon              | Group Description                                                                                                                                                                                                                |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>For:</u>       | Show/Hide Probe window.                                                                                                                                                                                                          |

|                   | Create new project, open created project, and save project.                                                                                                                                                                      |

|                   | These are run control icons used with the analyzer instrument. Use them to acquire, autorun/auto trigger, and halt an acquisition. The auto-trigger mode will continually trigger, capture, and re-arm for the next run capture. |

| 100 MHz ▼         | Use this pull down menu to choose synchronous or asynchronous  clocks. See Synchronous and Asynchronous.                                                                                                                         |

| Early (25%/75%) 🔻 | Select the trigger position from the pull-down menu                                                                                                                                                                              |

| HŞB LŞB LSB HSB   | Use these icons to create or undefine signal busses.                                                                                                                                                                             |

| Zoom 🗵            | Change the resolution of the timing analyzer display by zooming in or out.                                                                                                                                                       |

|                   | Displays acquisition data as a timing view or a state list. Timing view is displayed horizontally as a graph                                                                                                                     |

| Icon | Group Description                                      |

|------|--------------------------------------------------------|

|      | and the state list is displayed vertically as a table. |

### Main Window

Figure 15 · Silicon Explorer Main Window

The Silicon Explorer software presents information in rows and columns just like a spreadsheet. In the Timing Analyzer each row represents a channel or, in the case of bussed signals, group of channels. Each column contains specific information about that channel, such as the acquired data, trigger condition, signal activity indicator, etc. These columns may be moved and resized as desired.

### **Pattern Column**

The Pattern column contains logic levels and or edge conditions for each channel and can be named. These logic conditions are logically added together composing a pattern which can be used to trigger the analyzer, locate (find) similar patterns within the data, or highlight similar (or dissimilar) patterns

See Pattern for information on creating or renaming a pattern.

### Wire Number

The Wire Number column provides a reference between the signal name and the physical target cable assembly wire. In the case of bussed signals, this column contains the list (in order) of all channels included in the bus. This column can be moved or resized as needed.

### C1 and C2 (Level at cursor n)

The C1 and C2 columns display the logic levels of all visible channels at the time sample beginning with cursor 1 and cursor 2 respectively. For example, if you place cursor 1 on a logic transition, the C1 column will display the logic level immediately to the right of cursor1. This column can be moved or resized as needed.

# **Activity Indicator**

The Activity Indicator column provides a real time indication of the state of each channel. The states displayed are Constant HIGH level, Constant LOW level, and TOGGLING. In the case of bussed signals, the state of the last channel in the bus is displayed. This column can be moved or resized as needed.

Note: Note: Resizing this column is done by dragging the right edge of the column to the right and can only be done when it is not the last column on the right.

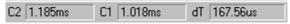

### **Readout Bar**

Cursor measurements are displayed in the Readout Bar located near the bottom of the screen.

Figure 16 · Readout Bar

C1 - Time (or number of clocks) from the trigger to cursor 1

C2 - Time (or number of clocks) from the trigger to cursor 2

dT - Time (or number of clocks) between cursor 1 and cursor 2

Time measurements appear on the readout bar automatically after cursors are placed in the data.

Figure 17 · C2 to trigger / C1 to trigger / C2 to C1

# **Shortcuts**

### **Keyboard Shortcuts**

Table 9 · Keyboard Shortcuts

| Menu                  | Action                     | Shortcut Key           |

|-----------------------|----------------------------|------------------------|

| Run Control           | Run                        | R                      |

|                       | Auto Trigger               | А                      |

|                       | Stop                       | S                      |

| Zoom (timing display) | Zoom in                    | Up arrow               |

|                       | Zoom out                   | Down arrow             |

|                       | Full screen                | Spacebar               |

| Pan Controls          | Next Screen                | Page down              |

|                       | Previous Screen            | Page up                |

| Timing                | Forward                    | Right arrow            |

|                       | Backward                   | Left arrow             |

| Goto                  | Trigger                    | Home                   |

|                       | Cursor 1                   | 1                      |

|                       | Cursor 2                   | 2                      |

|                       | Find cursor                | F                      |

|                       | Beginning or end           | End                    |

| Find                  | Next                       | Ctrl+F                 |

|                       | Previous                   | Ctrl+Shift+F           |

| Cursors               | Nudge cursor 1 forward     | Ctrl+right arrow       |

|                       | Nudge cursor 1<br>backward | Ctrl+ left arrow       |

|                       | Nudge Cursor 2 forward     | Ctrl+Shift+right arrow |

| Menu                                | Action         | Shortcut Key           |

|-------------------------------------|----------------|------------------------|

|                                     | Set cursor 1   | Ctrl+1                 |

|                                     | Set cursor 2   | Ctrl+2                 |

| Edit Controls                       | Undo           | Ctrl+Z                 |

|                                     | Cut            | Ctrl+X                 |

|                                     | Сору           | Ctrl+C                 |

|                                     | Paste          | Ctrl+V                 |

|                                     | Delete         | Del                    |

|                                     | Select all     | Ctrl+A                 |

|                                     | Deselect all   | Esc                    |

|                                     | Rename         | Enter                  |

| Wiggle Sticks: Place cursor in data | Course Control | Alt (move mouse)       |

| area                                | Fine Control   | Shift+Alt (move mouse) |

### **Context Menu Shortcut**

Context-sensitive menus are provided via the right mouse button. They are available for the rows and columns of the logic analyzer window.

# **Data Display**

The Silicon Explorer software contains an array of tools to format and view acquired data. These topics explain what the tools are, and how to use them.

- Bussed Signals

- Multiple Document Interface

- Timeline

- Rearrange Channels

# **Bussed Signals**

Channels may be grouped together as a bus, with their combined numeric value displayed in hex, decimal, ASCII or analog radix.

### **Creating a Bus**

Channels can be grouped together as a bus, with their combined numeric value displayed in hex, decimal, ASCII or analog radix.

Signal busses can be created by grouping similar channels together (such as data lines, address lines, etc.). Once created they can be undefined and viewed as individual channels again.

### To create a bus:

- 1. Click in the channel's wire number column to highlight the bus.

- 2. Click and drag the cursor to highlight the remaining channels.

- 3. Click the MAKE BUS icon on the tool bar.

### **Undefining a Bus**

### To undefine a bus:

- 1. Click the buses wire number column to highlight it

- 2. Click the Undefine Bus icon.

### Collapsing a Bus

Expanding a bus shows the individual channels without losing the bus structure that happens when the bus is Undefined. Collapsing the bus has the opposite affect, displaying the signals as a single bus once more.

### To Expand a bus:

- 1. Highlight the bus by clicking on the bus' wire number column.

- 2. Click the Expand Bus icon.

### **Expanding a Bus**

### To Collapse an Expanded bus:

- 1. Highlight the bus by clicking on the bus' wire number column.

- 2. Click the **Collapse Bus** icon.

### See Also

Radix

**Bus Ordering**

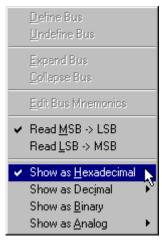

### **Radix**

The combined numeric values of bussed signals can be displayed in one of several radixes such as hexadecimal, binary, decimal, ASCII, analog and user mnemonics.

### To select a radix:

- 1. Highlight the bus by clicking in the bus' wire number column.

- 2. Select **Bus** from the menu bar.

- Click on the desired radix.

Figure 18 · Selecting Radix

Note: Note: The bus values will be incorrect if the order of the channels is backwards (MSB is in the LSB position). See Bus Ordering to correct the problem.

### **Bus Ordering**

Bus ordering refers to the order in which channels are selected when a bus is defined.

Problems with bus ordering become apparent after a bus is created and data is captured. If the bus order is backwards, the data will also be backwards and may be unintelligible. Silicon Explorer software provides a way to specify the bit order, even after the bus has been defined.

### To set the bus order:

- 1. Highlight the bus by clicking on the bus' wire number column.

- 2. Click the appropriate bus order icon.

### See Also

Radix

### **Multiple Document Interface**

The Multiple Document Interface lets users open several logic analyzer windows within the Silicon Explorer application. Each window is a unique analyzer session, containing its own trigger settings, channel labels,

data, etc. A window can also be a clone of another, containing the same data and settings, but with a different view (pan, zoom, etc.) of the data.

The active window has access to the logic analyzer hardware and is the only one that can capture acquisition data.

To create a copy of the current window, from the menu bar, select Window > New Window.

To create a new analyzer instrument, from the menu bar, select **File >New**, then click on the instrument desired.

To arrange the analyzer windows, from the menu bar, select Window, then Cascade or Tile.

### To switch between analyzer windows:

Click within the desired analyzer window

or

From the menu bar, select Window, then click on the desired window name.

### **Timeline**

A timeline is displayed along the top of the data display providing a time reference for acquired data. This reference can be presented in time units (seconds) or in samples. Additionally, vertical reference dots can be turned on (or off) providing a grid in the data display making time relationships between channels much easier to see.

### To display the timeline in seconds:

- 1. From the menu bar, select View >Timeline.

- 2. Click **Time Units** to place a check next to it.

### To display the timeline in samples:

- 1. From the menu bar, select View > Timeline.

- 2. Click Samples (Hex) or Samples (Decimal) to place a check next to the desired setting.

### To enable or disable the reference dots:

- 1. From the menu bar, select View.

- 2. Click Sample Dots to place a check next to it.

## Rearrange Channels

Channels can be rearranged so that related signals are displayed next to one another. Channel rearrange is also useful before grouping channels together as a bus.

### To move a channel:

- 1. Press and hold the Alt key.

- 2. Position the cursor over the channel to be moved. A hand displays.

- 3. Click and drag the channel to the desired location.

### Pattern

Pattern is a generic name describing a user defined template of logic conditions used for comparison with real data. Patterns may include any or all input channels, and are used for triggering, locating data and highlighting occurrences of data patterns.

### To create a new pattern:

- From the Pattern menu choose New Pattern. or

- Press the letter P on the keyboard.

### To modify the logic conditions:

- 1. Place the mouse cursor over the Pattern column for the input channel(s) of interest.

- 2. Click the mouse button to cycle through the list of choices. or

Right-click to display a list of choices and select an option from the drop-down menu.

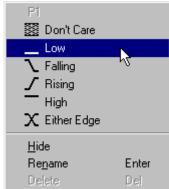

Figure 19 · Pattern Column

### To rename a pattern:

- 1. Click the pattern to highlight the pattern of interest.

- 2. Press Enter.

- 3. Type the new name and press **Enter**.

### **Find**

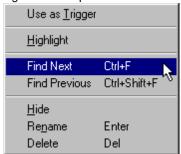

Patterns can be used as to locate occurrences of specific logic conditions within the acquisition data. Once the logic conditions of interest are entered into the pattern, the find operation can take place.

### Locating data using patterns:

- 1. Create a pattern containing the data conditions of interest.

- 2. Right-click the pattern name to select it.

3. Click Find Next or Find Previous . (You can also use the keyboard shortcuts Ctrl+F to Find and Ctrl+Shift+F to Find Previous.)

### See Also

**Pattern**

**Trigger**

Highlight

**Keyboard Shortcuts**

# Highlight

Silicon Explorer Patterns can be used to visually highlight the occurrence(s) of specified data patterns within acquisition memory.

### To highlight data that matches a pattern:

- 1. Create a pattern containing the data conditions of interest.

- 2. Clck the pattern heading (name) to highlight it.

- 3. Form the Pattern choose Highlight.

- 4. Acquisition samples that match the data pattern are highlighted.

### See Also

Find

**Trigger**

**Keyboard Shortcuts**

### **Data Files**

Previously acquired data files can be opened for viewing and analysis. When saved, the files are given a ".bce" extension.

### To open a file:

- From the File choose Open.

- Select Pod-A-Lyzer Files (\*.bce) in the Files of Type box

- · Click the desired file

- Click File Open icon

To close a file, from the File choose Close.

Acquisition data and setup information, such as the trigger condition, channel labels, etc., are stored together when saved to a file. This way, the analyzer display always looks the same as when it was last used.

To save a data file, from the File menu choose Save or click the Save icon.

Use the **Print** command to print an active window in Silicon Explorer.

# Copy Display Data

State list display data may be copied, then pasted into an ASCII file in a tab-delimited format.

### To copy state list data:

- 1. Place the mouse cursor over the wire number of the first column of data to be selected.

- 2. Click and drag the mouse to highlight all the data columns.

- 3. From the **Edit** choose **Copy**.

### Readback Data

Data captured by an analyzer device is automatically transferred to the PC. It is sometimes useful to read that data again.

### To readback data:

From the Instrument menu choose Readback Data. Instrument and then choose Readback Data.

### See Also

Run Controls

• Multiple Document Interface

# **Logic Analyzer Concepts**

# **Synchronous Sampling**

Synchronous sampling is supported only on Silicon Explorer I. Silicon Explorer II does not support synchronous sampling. Synchronous sampling uses a sample clock that is external to the logic analyzer - usually the clock from the system under test. This mode of operation is often referred to as State acquisition since the analyzer is capturing the state of all signals on every clock. The target clock must be connected to the wire labeled **CLKIN**. The clock ground wire must be connected for best signal integrity at high clock rates ( > 20MHz ). The Silicon Explorer does not require the clock to be an oscillator. However, it does require a continuous series of edges for operation.

State Display is a tabular display of logic activity, usually captured synchronously to an external clock. The data displayed on each horizontal line represents one recorded sample. The analyzer can display the recorded data in a variety of <u>radixes</u> (numerical formats) including binary, decimal, hexadecimal, analog, etc.

Clock Qualifier

| ate#         | Si      | gna    | l Name        | s      |        |            |

|--------------|---------|--------|---------------|--------|--------|------------|

| #            | 0       | 1      | 2:9           | 10     | 11     | 12:17      |

| Name         | Vblank- | Vsync- | Video Addres: | Hblank | Hsync- | Horiz Data |

| 4C93<br>4C94 | 1       | 1      | DD<br>DD      | 0      | 0      | 30<br>20   |

| 4095         | 1       | 1      | DD            | 0      | 0      | 01         |

| 4096         | 1       | 1      | DD            | 0      | 0      | 02         |

| 4097         | 1       | 1      | DD            | 0      | 0      | 05         |

| 4098         | 1       | 1      | DE            | 0      | 1      | 0B         |

| 4099         | 1       | 1      | DE            | 0      | 1      | 17         |

| 4C9A         | 1       | 1      | DE            | 0      | 1      | 2E         |

| 409B<br>4090 | 1       | 1      | DE<br>DE      | 0      | 1      | ID<br>3A   |

| 4090<br>409D | 1       | 1      | DE            | 0      | 1      | 35         |

| 4C9E         | 1       | 1      | DE            | 0      | 1      | 2A         |

| 4C9F         | 1       | 1      | DE            | ō      | 1      | 14         |

| 4CA0         | 1       | 1      | DE            | 0      | 1      | 29         |

The Clock Qualifer is an external signal that acts as a gate for the acquisition clock. When the external signal is false, the acquisition clock is not allowed to load acquired data into acquisition memory.

The Clock Qualifier is useful when you want to observe signal activity taking place only when a particular chip is selected. For example, if the system under test has three devices of the same type connected to a common bus, one of which appears to be defective, you might want to record signal activity on the bus only when the suspect device is selected.

If the logic analyzer's Clock Qualifier input were connected to the chip select line of the device we were interested in, the analyzer would record data only when the chip's select line was active. The Clock Qualifier allows us to filter out irrelevant data by only clocking data of interest into the sample buffer.

### To set up for Synchronous acquisition:

- 1. Connect the clock leads of the Target Cable Assembly to the target circuit clock signal.

- From the Instrument menu, choose Clock > Clock Edge and click either Rising or Falling depending on which edge is appropriate.

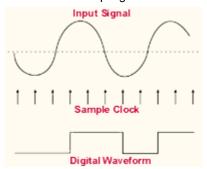

# Asynchronous Sampling

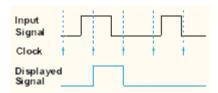

An acquisition that is made using a clock signal generated internally by the analyzer. This clock is unrelated to the clock in the target system, and can be set by you.

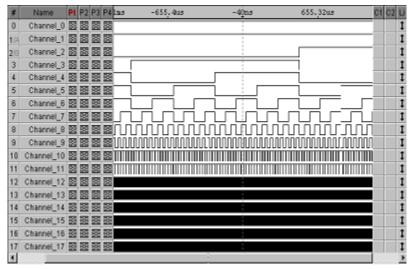

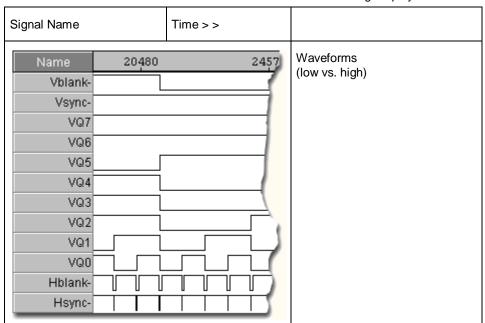

### **Timing Display**

Timing display is a graphic representation of the timing relationships between input signals, displaying the recorded signal activity in timing diagram format. The screen fragment below shows a typical timing display in which multiple signals are displayed one on top of another. This type of display is ideal for understanding the "logic level vs. time" relationships between multiple channels at a single glance. Measuring the time between signal events is usually accomplished with the use of cursors.

Table 10 · Timing Display

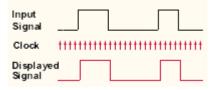

### **Sample Rate**

Sample rate is the speed at which the input signals are sampled, often expressed in mega-samples per second (MSa/s). Selecting the proper sample rate is important to ensure that signals are displayed accurately, and completely.

Figure 21 · Signal with Narrow Pulse

The example above shows a signal containing a narrow pulse at the end. In the case above, it is being sampled fast enough to capture the pulse. If the sample rate were slowed down, however, it would be possible to miss the narrow pulse entirely, as shown below.

Figure 22 · Signal with Slowed Rate

To get adequate sample resolution, a good "rule of thumb" is to make sure the analyzer samples 4 to 10 times faster than the fastest signal being captured.

For example, if you wanted to capture a 40 nanosecond (ns) pulse, you would want the analyzer to sample at least 4 times faster ( 40ns/4 = 10ns). Sampling 10 times faster may not be practical since it would require an analyzer that samples every .4ns, or 2.5 giga-samples per second (GSa/s).

### Capturing the entire signal

Logic analyzer sample buffers usually have a "fixed" size. This means that the faster memory is filled (the faster the sample rate), the shorter the overall acquisition time will be.

If you need to capture a burst of data that lasts 5 ms. Let's also assume the sample buffer can store 64K samples (actually 65536 samples since 64K is really 2^16). Simply divide 5ms by 65536 which results in 76.3 ns. In other words, with a 64K sample buffer and the analyzer sampling at 76 ns, it will capture 5 ms worth of signal activity.

In reality the analyzer probably has fixed sample rate steps (such as 200 ns, 100 ns, 50 ns, 20 ns, etc.). To comply with the requirements in the example above, we would not be able to sample faster than 76.3 ns and still capture 5 ms worth of data. The closest alternative would be 100 ns, which would result in 6.6 ms worth of data (65536 samples x 100 ns). Assuming 100 ns is fast enough to sample the input 4 times faster than the fastest signal (100 ns  $^*$  4 = 400 ns pulse), we will meet our objectives for sample resolution and acquisition length.

### **Sample Resolution**

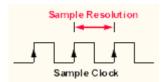

Sampling Resolution is the interval (in seconds) between samples, determined by the frequency of the sample clock. Suppose, for example, that the sample clock was running at 100 MHz, and we were sampling on the rising edge as shown below. The sample resolution would be 1/100 MHz, or 10 ns.

Figure 23 · Sample Resolution

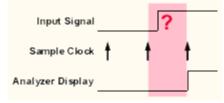

When the timing analyzer samples an input line, it is either high or low. If the line is at one state (high or low) on one sample and the opposite state on the next sample, the analyzer "knows" that the input signal transitioned sometime in between the two samples. It doesn't know when, so it places the transition point at the last sample, as shown below.

Figure 24 · Sample Uncertainty

This presents some uncertainty as to when the transition actually occurred and when it is displayed by the analyzer. Worst case for this uncertainty is one sample period, assuming that the transition occurred immediately after the previous sample point.

# **Understanding Triggering**

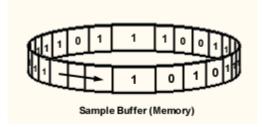

Triggering is the process of halting the logic analyzer after a specific event has occurred. The event is typically called a trigger pattern and is the logical and of logic conditions on one or more channels. In multi-level triggering, several logic events may be required to occur before the analyzer triggers.

It is helpful to understand how acquisition memory applies to the trigger process:

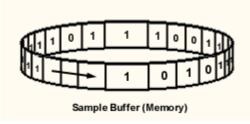

Conceptually, the acquisition memory acts as a circular buffer. Once the analyzer is started, samples are stored in sequence. If the analyzer fills memory before a trigger occurs, it will continue to acquire data with the newest data over-writing the oldest. Once a trigger occurs, the analyzer will either:

- 1. Stop immediately acquisition memory contains waveform data of signal activity leading up to the trigger only (also called pre-trigger data).

- 2. Fill the entire memory once more acquisition memory contains waveform data of signal activity that occurred after the trigger (also called post-trigger data).

- Fill only a portion of memory acquisition memory contains both pre-trigger and post trigger information.

# **Trigger**

By default, the Silicon Explorer software contains a trigger pattern, identified by a red font. Other patterns, however, can be selected for use as the trigger pattern.

### Selecting a pattern to trigger the analyzer:

- 1. Click the pattern of interest to highlight it.

- 2. From the **Pattern** choose **Use as Trigger**. The pattern name is displayed in a red font signifying that this is now the trigger pattern.

#### See Also

**Pattern**

Find

**Highlight**

# **Auto-Trigger**

Auto-trigger lets you view the captured data dynamically. Acquisitions are made, the display updated and the analyzer started for the next capture automatically. The rate at which the display is updated depends upon the amount of data being viewed and the frequency of the trigger event. The fastest update is about once every second.

### To start auto-trigger:

- Toolbar: Click the AUTO TRIGGER icon.

- From the Instrument menu choose Run Auto Trigger.

- Keyboard: Press the letter A.

### To halt auto-trigger:

- Toolbar: Click the HALT icon.

- From the Instrumentmenu choose Stop.

- Keyboard: Press the letter S.

#### See Also

**Understanding Triggering**

# **Triggering**

The Silicon Explorer software supports both single-level and multi-level triggering depending on whether you are connected to a Silicon Explorer or a Silicon Explorer II. Select the device you are using from the list in the device menu.

# Triggering Silicon Explorer

The Silicon Explorer has a single-level trigger sequence with a selectable trigger position. Silicon Explorer II has up to four-levels in its trigger sequence.

## **Trigger Pattern**

A trigger pattern is the logical AND of the trigger conditions set on all 18 channels. Each channel may be set to one of the following trigger conditions:

- Don't Care

- High

- Low

- Rising Edge

- Falling Edge

- Either Edge

#### To set the trigger condition for a single channel:

Right-click the trigger pattern column of the desired channel and choose the trigger condition.

#### To set the trigger pattern for a group of bussed signals:

- 1. Click the Trigger Pattern column of the channel bus.

- 2. Enter the pattern using the keyboard, using the same radix as the bus.

#### To select a pattern to trigger the analyzer:

- 1. Click to select the pattern of interest.

- 2. From the **Pattern** menu choose **Use as Trigger**. The pattern name is displayed in a red font, indicating that this is now the trigger pattern.

## **Trigger Position**

The Trigger Position controls determines how much of the captured data came before the trigger and how much came after. There are three possible settings:

- Early (25% pre, 75% post)

- Center (50% pre, 50% post)

- Late (75% pre, 25% post)

#### To set the trigger position from the menu bar:

- 1. On the Instrument menu select Trigger Position

- 2. Click on the desired position (Early, Center, or Late)

## See Also

**Understanding Triggering**

# **Analyzer Controls**

## **Probe Instrument**

Probe files are generated from Designer software and contain device information, net names, and node location information. This information is displayed in a tree structure for verification. For Axcelerator devices, the net name is prefixed by the tile number the module is on. e.g. net <0,1>ALU\_test\_mod\_d is .on tile 0,1.

Once a \*.prb file is opened and a device connection has been made then the checksum of the target device can be read and compared against the checksum in the file. This ensures that the selected probe file matches the target device.

Figure 25 · Display for non-Axcelerator Devices

Figure 26 · Display for Axcelerator devices

## **Open a Probe File**

Note: Note: Designer R398 or later is required. (Designer R1-2002 SP2 or later is required for Axcelerator)

#### To open a file:

- 1. From the **File** menu choose **Open > Files of type** (\*.prb).

- 2. Double click the desired probe file.

## Assign a Probe

#### To assign a node to a probe:

- 1. Click the node to select it.

- 2. Click the PRA or PRB button. (PRA, PRB, PRC, or PRD for Axcelerator devices)

The selected node is routed to the probe pin and the corresponding analyzer input switched to the debug connector. The net name will also appear in the waveform window.

Note: Note: For Axcelerator devices, only the Probe A and Probe B pins will be automatically switched to the corresponding analyzer input. You must connect the Probe C and Probe D pins to CH3 and CH4 respectively. The net names for Probe C and Probe D automatically appear in the current waveform window for CH3 and CH4 unless you have already typed a name for the channel.

## **Display Features**

The tree control lists the nets or pins in the design. To format the display, right-click the Nets branch. Use the FILTER field to filter the list. Wildcards (\* ?) are supported.

A history is maintained on the probe and filter lists (PRA, PRB, PRC, PRD, and FILTER) accessible from the pull-down button.

## **Run Controls**

Several controls are provided to start and stop the analyzer instrument, including an auto-trigger mode which continually triggers, captures and re-arms for the next capture. Facility is also provided to readback data from the instrument which is very useful when using <u>multiple analyzer windows</u>.

#### To start an acquisition:

Tool bar: Click the RUN icon

From the Instrument choose Run

Keyboard: Press the letter R

#### To halt an acquisition:

Tool bar: Click the HALT icon

From the Instrument menu choose Stop

Keyboard: Press the letter S

#### See Also

Auto-Trigger Readback Data

# Sampling

Signals may be sampled synchronously, using an external clock, or asynchronously, using the logic analyzer's internal clock. Sample rate specifications are listed in the <u>specifications</u> section of the online help.

#### To set up for synchronous acquisition:

- 1. Connect the clock leads of the Target Cable Assembly to the target circuit clock signal.

- 2. From the Instrument menu, choose **Clock > Clock Edge** and click either **Rising** or **Falling** depending on which edge is appropriate.

## To set the asynchronous sample rate from the tool bar:

- 1. From the Instrument menu, choose Clock.

- 2. Scroll down the list of sample rates until the desired rate is selected, then click the left mouse button.

#### To set the asynchronous sample rate from the menu bar:

- 1. From the **Instrument**menu, choose **Clock**.

- 2. Scroll down the list of sample rates until the desired rate is selected, then click select it.

#### See Also

<u>Understanding Synchronous Sampling</u> <u>Understanding Asynchronous Sampling</u>

# **Troubleshooting Silicon Explorer**

# **Troubleshooting Errors**

## Q&A

| Q1 | I've connected Silicon Explorer and the waveform window display reads POLL.               |

|----|-------------------------------------------------------------------------------------------|

|    | Look on the top of the Silicon Explorer for the flashing yellow "heartbeat", if it is not |

| Q2 | It's flashing but still POLL.                                                                                                |

|----|------------------------------------------------------------------------------------------------------------------------------|

| A2 | There are a number of things that can prevent communication from being established. The following are the most common:       |

|    | Wrong COM port. Try all four COM ports even though you are sure that your mouse is on COM 1.                                 |

|    | No power to the analyzer.                                                                                                    |

|    | Desktop systems external COM connector not connected to the COM port internally.                                             |

|    | Laptop systems external COM connector disabled (IR Port Override?). Use your PC's CMOS setup program to enable the COM port. |

|    | COM port IRQ reassigned for DOS program, control panel not updated.                                                          |

|    | Multiple mouse drivers in system.ini.                                                                                        |

|    |                                                                                                                              |

| Q3 I've got the IDLE message but when I click RUN, the Waveform will error message and returns to IDLE. |  | I've got the IDLE message but when I click RUN, the Waveform window flashes an error message and returns to IDLE.                                                                                               |

|---------------------------------------------------------------------------------------------------------|--|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                         |  | If the target power is incapable of supplying the necessary current, then the Waveform window resets and returns to IDLE. Many current-limiting supplies will trip when set too close to the operating current. |

Third-party serial port "enhancers" not conforming to windows API.

| Q4 | The Waveform window acquires data and then indicates errors on readback.                                                                                                                                                                 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A4 | The Waveform window bursts data back in blocks at high speed, with built-in retry for a bad block (both checksum and byte count are used). Some third-party serial programs block all interrupts forcing the analyzer into a retry loop. |

|    | Some laptops power down the UART and drop a few characters. Try disabling "Power Saving" in the CMOS setup menu.                                                                                                                         |

Q5 When the Waveform window is open, my other Windows programs run slowly.

- A5 If the Waveform window is open but it is not connected or powered up, then the system is constantly timing out looking for a response. Either close the Waveform window or change the COM port to DEMO.

- Q1 The Analyze module acquires data and then indicates errors on read-back. Why?

- A1 The Analyze module bursts data back in blocks at high speeds, with built-in retry for a bad block (it uses both checksum and byte count). Some third-party serial programs block all interrupts, forcing the analyzer into a retry loop. Some laptops power down the UART and drop a few characters. Try disabling "Power Saving" in the CMOS setup menu.

- Q When the Explore window is open, my other Windows programs run slowly. Why?

- If the Explore window is open but not connected or powered up, then the system is constantly timing out looking for a response. Either close the SE II window or change the COM port to DEMO.

- Q I get a message "Device Timed out" when I try to assign a particular signal to the Probe pins. Why?

- This message gives us an indication that the power is not sufficient for the Silicon Explorer and as a solution you would have to add a separate power source for the Silicon Explorer. Refer to Powering Silicon Explorer II for more information.

- Q I have assigned an internal signal to PRA and PRB but the PRA and PRB light is not blinking on the Probe Pilot. Is this normal?

- The PRA and the PRB light on the Probe Pilot are just an indication of the logic level of that assigned internal signal. If the assigned internal net is at permanent logic 0, the light on the Probe Pilot for the corresponding probe will not glow.

- Q Where are my TMS and SDO pins?

- A Your cable will not have the TMS and the SDO pins if it was bought before the SX probing capability was introduced. To order a new cable (Si-Ex-Ribbons), contact Actel customer service at Customer.Service@actel.com.

- Q Is the Silicon Explorer displaying an incorrect signal?

- A Make sure that the signal is sampled at a sufficiently high frequency. The sampling rate should be at least twice the frequency of the fastest changing signal. The maximum frequency at which the signal can be sampled is 100 MHz which limits the frequency of the device to 50 MHz. If a higher sampling frequency is required than the PRA and the PRB pins can be connected to a logic analyzer to view the signals.

- Q Why can't I find the net I wish to probe?

- A Silicon Explorer lists only the signals that are actually present on the device. There is a possibility that the net which you wish to probe has been optimized in Designer. Please check the list of the nets combined in the combiner file (\*.cob) which is exported from Designer File > Export > Auxillary File with file type \*.cob

- Q What are the limitations in probing devices using Silicon Explorer?

- A Probing limitations are described in the table below. Note that -- indicates that the feature is unavailable, and \* indicates that the feature only applies to devices that have Qclock.

Figure 27 · Probing Limitations

| Family       | Probe Capable |       |        |        |

|--------------|---------------|-------|--------|--------|

|              | Input         | Clock | Hclock | Qclock |

| ACT1/40MX    | Y             | Υ     |        |        |

| ACT2/XL/42MX | Υ             | Υ     |        |        |

| ACT3         | Υ             | Υ     | Υ      |        |

| DX/42MX      | Υ             | Υ     |        | Y*     |

| SX/SX-A/eX   | N             | Υ     | N      | N*     |

# **Troubleshooting General**

The following is a list of frequently asked questions.

- Q Does Silicon Explorer support ProASIC programming and debugging?

- A No. As of today Silicon Explorer does not support either ProASIC programming or debugging.

- Q Can we use Silicon Explorer to debug devices which have their security fuses programmed?

- A As a part of the FPGA security feature the Silicon Explorer cannot be used on devices which have their security fuse programmed.

# **Troubleshooting Software**

Q How do I set up triggering?

- A You have an option of setting trigger either EARLY that displays the values in the ratio of (25% 75%), where the first % represents the % of data sampled before the trigger point and the later % represent % sampled after the trigger point. The other options available are CENTER(50% 50%) and LATE(75% 25%). You can select the trigger position from Instrument -> Trigger Position and then selecting the required Trigger position.

- Q What is the recommended sampling rate?

- For an accurate reading, the sampling rate for a particular signal should be at least twice the rate at which the signal is changing (According to the Nyquist theorem). For example, a clock operating at 25 MHz should be sampled at least 50 MHz frequency. Be aware that sampling at higher frequencies causes the Silicon Explorer to consume more power.

- Q What is the best way to find nets?

- A The best way to find the nets in the Silicon Explorer is to use the Filter option available in the software. You can search for the net you require by using the \*partial\_name\* in the filter, which would return all the signals having that partial\_name of the net. If you are using an HDL flow, it may be difficult to recognize the net names you need to observe. Microsemi recommends that you use a synthesis tool that can generate a gate-level schematic of your synthesized netlist so that during probing, you can easily trace through the schematic and obtain the net names from it.

# Troubleshooting Hardware

- Q How do I probe an SX-A device?

- The probing of an SX-A device requires special setup because it requires a 70 ohm termination on all the probe connectors (TDI, TDO, TCK, TMS, PRA, PRB). The 70 ohm series termination is used to prevent data transmission corruption during probing.

- Q How do I tie the TRST pin during the probing using Silicon Explorer?

- A TRST is an active low input. During JTAG mode and Silicon Explorer debugging mode, JTAG state machine's reset must not be active, otherwise probe circuitry is disabled. The recommendation for TRST pin in JTAG and Silicon Explorer is listed below:

RTSX Rev0 - No TRST pin RTSX Rev1 - You must tie TRST pin high when doing JTAG and Silicon Explorer.