# **inter<sub>sil</sub>**

### DATASHEET

## **Dual 20A/Single 40A Step-Down Power Module**

### **ISL8240M**

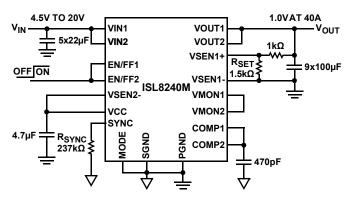

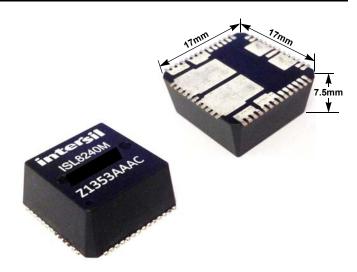

The ISL8240M is a fully-encapsulated step-down switching power supply that can deliver up to 100W output power from a small 17mmx17mm PCB footprint. The two 20A outputs may be used independently or combined to deliver a single output of 40A. Designing a high-performance board-mounted power supply has never been simpler – only a few external components are needed to create a very dense and reliable power solution.

**1.5%** output voltage accuracy, differential remote voltage sensing and fast transient response create a very high-performance power system. Built-in output overvoltage, overcurrent and over-temperature protection enhance system reliability.

The ISL8240M is available in a thermally-enhanced QFN package. Excellent efficiency and low thermal resistance permit full power operation without heat sinks or fans. In addition, the QFN package with external leads permits easy probing and visual solder inspection.

### **Related Literature**

AN1922, "ISL8240MEVAL4Z Dual 20A/Optional 40A Cascadable Evaluation Board Setup Procedure"

AN1923, "ISL8240MEVAL3Z 40A, Single Output Evaluation Board Setup Procedure"

### **Features**

- Fully-encapsulated dual step-down switching power supply

- Up to 100W output from a 17mmx17mm PCB footprint

- Dual 20A or single 40A output

- Up to 94% conversion efficiency

- 4.5V to 20V input voltage range

- 0.6V to 2.5V output voltage range

- 1.5% output voltage accuracy with differential remote sensing

- Output overvoltage, overcurrent and over-temperature protection

- QFN package with exposed leads permits easy probing and visual solder inspection

### **Applications**

- Computing, networking and telecom infrastructure equipment

- · Industrial and medical equipment

- · General purpose point-of-load (POL) power

NOTE: All pins not shown are floating

#### FIGURE 1. COMPLETE 40A STEP-DOWN POWER SUPPLY

FIGURE 2. SMALL FOOTPRINT WITH HIGH POWER DENSITY

### **Table of Contents**

| Pinout Internal Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Thermal Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Typical Performance Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Efficiency Performance.    10      Transient Response Performance.    11      Start-up and Short Circuit Performance .    13                                                                                                                                                                                                                                                                                                                                                                                      |

| Typical Application Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Programming the Output Voltage    21      Selection of Input Capacitor    21      Selection of Output Capacitors    21      EN/FF Turn ON/OFF    21      Thermal Considerations    22                                                                                                                                                                                                                                                                                                                             |

| Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

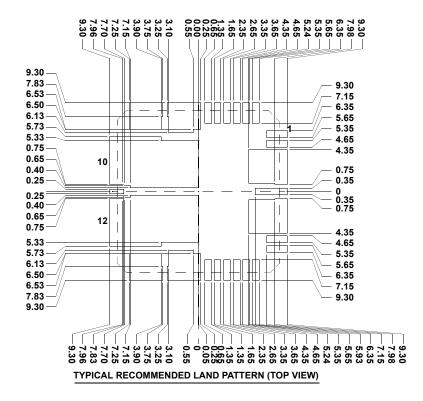

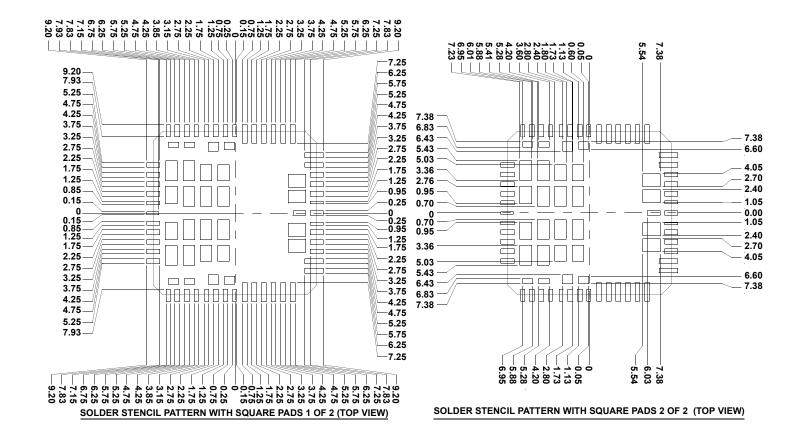

| Initialization22Enable and Voltage Feed-forward22Soft-Start.23Power-Good23Current Share23Overvoltage Protection (OVP)24Over-Temperature Protection (OTP)24Overcurrent Protection (OCP)24Overcurrent Protection (OCP)24Overcurrent Protection (OCP)24Overcurrent Protection (OCP)24Overcurrent Protection (OCP)24Overcurrent Protection (OCP)24Prequency Synchronization and Phase Lock Loop24Tracking Function25Layout Guide25Current Derating26PCB Layout Pattern Design26Thermal Vias26Stencil Pattern Design26 |

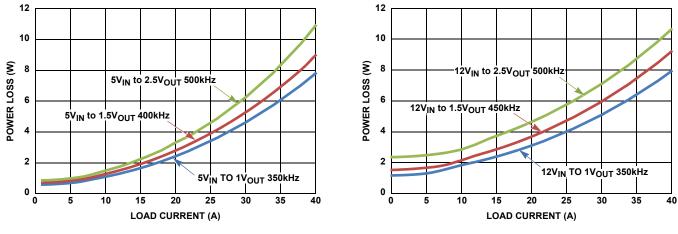

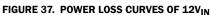

| Power Loss Curves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

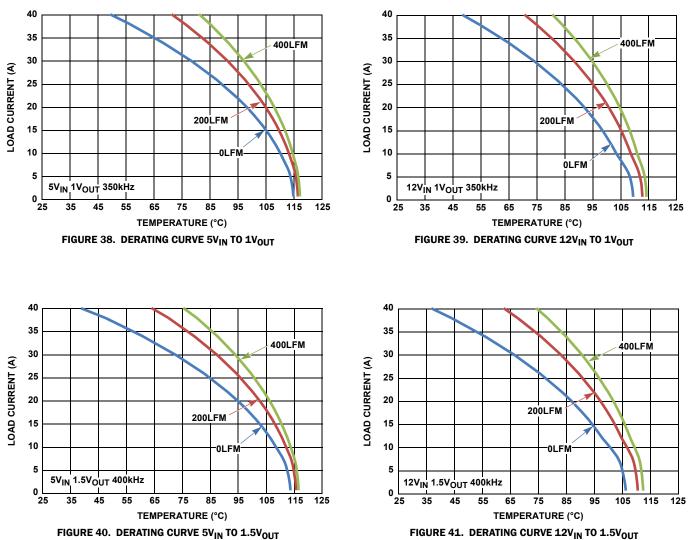

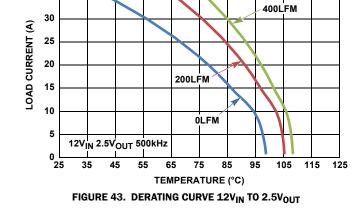

| Derating Curves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Reflow Parameters 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| About Intersil                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

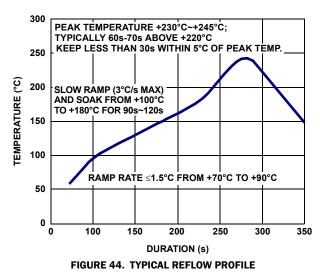

| Package Outline Drawing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

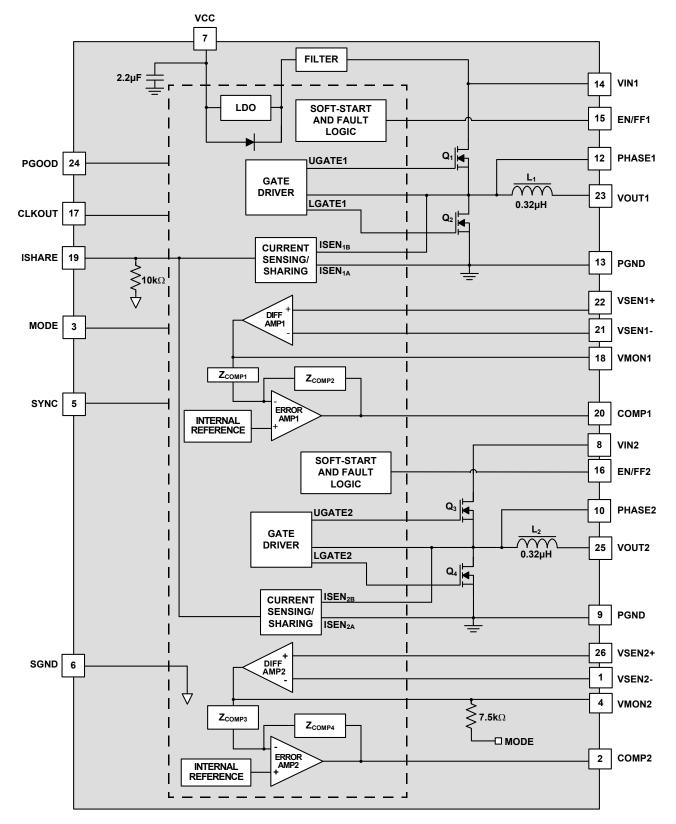

### **Pinout Internal Circuit**

### **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING      | TEMP. RANGE (°C)<br>( <u>Note 4</u> ) | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |  |  |  |

|--------------------------------|----------------------|---------------------------------------|-----------------------------|----------------|--|--|--|

| ISL8240MIRZ                    | ISL8240M -40 to +125 |                                       | 26 Ld QFN                   | L26.17x17      |  |  |  |

| ISL8240MEVAL3Z                 | Evaluation Board     |                                       |                             |                |  |  |  |

| ISL8240MEVAL4Z                 | Evaluation Board     |                                       |                             |                |  |  |  |

NOTES:

1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

These Intersil Pb-free plastic packaged products are RoHS compliant by EU exemption 7C-I and employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3) termination finish which is compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see product information page for ISL8240M. For more information on MSL, please see tech brief TB363

4. The ISL8240M is guaranteed over the full -40°C to +125°C internal junction temperature range. Note that the allowed ambient temperature consistent with these specifications is determined by specific operating conditions, including board layout, cooling scheme and other environmental factors.

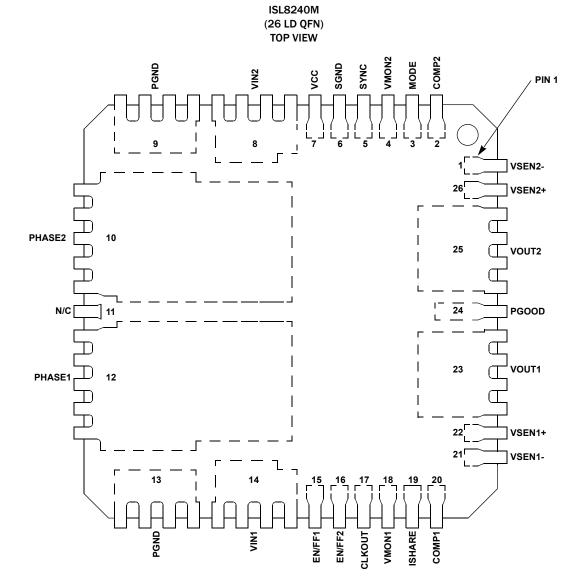

### **Pin Configuration**

### **Pin Descriptions**

| PIN<br>NUMBER | PIN<br>NAME       | TYPE | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|-------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21, 1         | VSEN1-, VSEN2-    | I    | <b>Output voltage negative feedback.</b> Negative input of the differential remote sense for the regulator. Connect to the negative rail or ground of the load/processor, as shown in Figure 24. The negative feedback pins can be used to program the module operation conditions. See Tables 3 and 5 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 20, 2         | COMP1, COMP2      | I/0  | <b>Error amplifier outputs.</b> Typically floating for dual-output use. For parallel use, a 470pF~1nF capacitor is recommended on the COMP pins of each SLAVE phase to eliminate the coupling noise. All COMP pins of SLAVE phases need to tie to MASTER phase COMP1 pin (first phase). Internal compensation networks are implemented for working in the full range of I/O conditions.                                                                                                                                                                                                                                                                                                                                                                                |

| 3             | MODE              | I    | <b>Mode setting.</b> Typically floating for dual-output use; tie to SGND for parallel use. See <u>Tables 3</u> and <u>5</u> for details. When VSEN2- is pulled within 700mV of VCC, the 2nd channel's remote sensing amplifier is disabled. The MODE pin, as well as the VSEN2+ pin, determine relative phase-shift between the two channels and the CLKOUT signal output.                                                                                                                                                                                                                                                                                                                                                                                             |

| 18, 4         | VMON1, VMON2      | I/0  | <b>Remote sensing amplifier outputs.</b> These pins are connected internally to OV/UV/PGOOD comparators, so they can't float when the module works in multiphase operation. When VSEN1-, VSEN2- are pulled within 700mV of VCC, the corresponding remote sensing amplifier is disabled; the output (VMON pin) is in high impedance. In this event, the VMON pins can be used as an additional monitor of the output voltage, with a resistor divider to protect the system against single point of failure. The default setting voltage is 0.6V. See <u>Table 3</u> for details.                                                                                                                                                                                       |

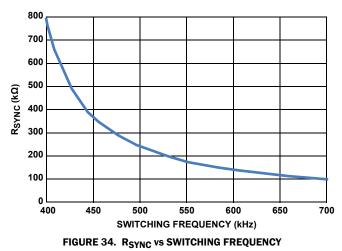

| 5             | SYNC              | I    | <b>Signal synchronization.</b> An optional external resistor (R <sub>SYNC</sub> ) connected from this pin to SGND increases oscillator switching frequency ( <u>Figure 34</u> and <u>Table 1</u> ). The internal default frequency is 350kHz with this pin floating. Also, the internal oscillator can lock to an external frequency source or the CLKOUT signal from another ISL8240M. Input voltage range for external source: 3V to 5V square wave. No capacitor is recommended on this pin.                                                                                                                                                                                                                                                                        |

| 6             | SGND              | PWR  | <b>Control signal ground.</b> Connect to PGND under the module in the quiet inner layer. Make sure to have the single location for the connection between SGND and PGND to avoid noise coupling. See <u>"Layout Guide" on page 25</u> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7             | VCC               | PWR  | 5V internal linear regulator output. Voltage range: 3V to 5.6V. The decoupling ceramic capacitor for the VCC pin is recommended to be 4.7μF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14, 8         | VIN1, VIN2        | PWR  | <b>Power Inputs.</b> Input voltage range: 4.5V to 20V. Tie directly to the input rail. VIN1 provides power to the internal linear drive circuitry. When the input is 4.5V to 5.5V, VIN should be tied directly to VCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9, 13         | PGND              | PWR  | Power ground. Power ground pins for both input and output returns.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12, 10        | PHASE1,<br>PHASE2 | PWR  | <b>Phase node.</b> Use for monitoring switching frequency. Phase pins should be floating or used for snubber connections. To achieve better thermal performance, the phase planes can also be used for heat removal with thermal vias connected to large inner layers. <u>See "Layout Guide" on page 25.</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11            | NC                | -    | Non-connection pin. This pin is floating with no connection inside.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

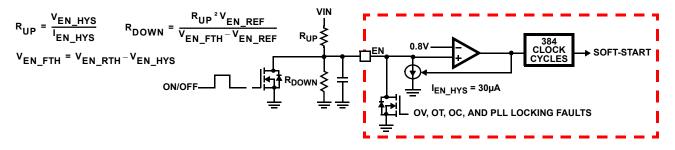

| 15, 16        | EN/FF1,<br>EN/FF2 | I/0  | <b>Enable and feed-forward control.</b> Tie a resistor divider to VIN or use the system enable signal for this pin. The voltage turn-on threshold is 0.8V. With a voltage lower than the threshold, the corresponding channel can be disabled independently. By connecting to VIN with a resistor divider, the input voltage can be monitored for UVLO (undervoltage lockout) function. The voltage on each EN/FF pin is also used to adjust the internal control loop gain independently to realize the feed-forward function. Please set the EN/FF between 1.25V to 5V. A 1nF capacitor is recommended on each EN/FF pin. Please see <u>Table 1</u> on <u>page 19</u> to select a resistor divider and application details in <u>"EN/FF Turn ON/OFF"</u> on page 21. |

| 17            | CLKOUT            | I/0  | <b>Clock out.</b> Provide the clock signal for the input synchronization signal of other ISL8240Ms. Typically tied to VCC for dual-output use with 180° phase-shift. See <u>Tables 3</u> and <u>5</u> when using more than one ISL8240M. When the module is in dual-output mode, the clock-out signal is disabled. By programming the voltage level of this CLKOUT pin, the module can work for DDR/tracking or as two independent outputs with selectable phase-shift. See <u>Table 6</u> .                                                                                                                                                                                                                                                                           |

| 19            | ISHARE            | 0    | <b>Current sharing control.</b> Tie all ISHARE pins together when multiple modules are configured for current sharing and share a common current output. The ISHARE voltage represents the average current of all active and connected channels. A 470pF capacitor is recommended for each ISHARE pin for multiple phase applications. Typically, the ISHARE pin should be floating for dual-output or single module application.                                                                                                                                                                                                                                                                                                                                      |

| 22, 26        | VSEN1+,<br>VSEN2+ | I    | <b>Output voltage positive feedback.</b> Positive inputs of differential remote sense for the regulator. A resistor divider can be connected to this pin to program the output voltage. It is recommended to put the resistor divider close to the module and connect the kelvin sensing traces of VOUT and VSEN- to the sensing points of the load/processor; see Figure 24. The VSEN2+ pin can be used to program the module operation conditions. See Tables 3 and 5 for details.                                                                                                                                                                                                                                                                                   |

| 23, 25        | VOUT1, VOUT2      | PWR  | Power Output. Apply output load between these pins and PGND pins. Output voltage range: 0.6V to 2.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

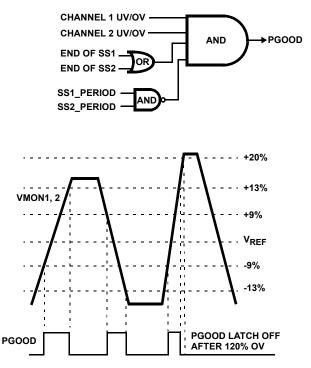

| 24            | PGOOD             | 0    | <b>Power-good.</b> Provide open-drain power-good signal when the output is within 9% of the nominal output regulation point with 4% hysteresis (13%/9%) and soft-start complete. PGOOD monitors the outputs (VMON) of the internal differential amplifiers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### **Absolute Maximum Ratings**

| Input Voltage, V <sub>IN</sub> -0.3V to +25V        Driver Bias Voltage, V <sub>CC</sub> -0.3V to +6.5V        Phase Voltage, V <sub>PHASE</sub> -0.3V to +30V        Input, Output or I/O Control Voltage      -0.3V to V <sub>CC</sub> + 0.3V |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ESD Rating<br>Human Body Model (Tested per JESD22-A114E) 2kV                                                                                                                                                                                    |

| Machine Model (Tested per JESD22-A115-A)    200V      Charge Device Model (Tested per JESD22-C101C)    750V      Latch-up (Tested per JESD-78B; Class 2, Level A)    100mA                                                                      |

#### **Thermal Information**

| Thermal Resistance (Typical)      | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C∕W) |

|-----------------------------------|------------------------|------------------------|

| QFN Package (Notes 5, 6)          | 8.5                    | 0.9                    |

| Maximum Storage Temperature Range |                        | 5°C to +150°C          |

| Pb-free Reflow Profile            | Rei                    | fer to Figure 44       |

#### **Recommended Operating Conditions**

| Input Voltage, V <sub>IN1</sub> and V <sub>IN2</sub>    |                |

|---------------------------------------------------------|----------------|

| Output Voltage, V <sub>OUT1</sub> and V <sub>OUT2</sub> | 0.6V to 2.5V   |

| Junction Temperature Range                              | 40°C to +125°C |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

5. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief <u>TB379</u>.

6. For  $\theta_{JC}$ , the "case temp" location is the center of the phase exposed metal pad on the package underside.

**Electrical Specifications**  $T_A = +25$  °C,  $V_{IN} = 12V$ , unless otherwise noted. Boldface limits apply across the internal junction temperature range, -40 °C to +125 °C (Note 4).

| PARAMETER                              | SYMBOL               | TEST CONDITIONS                                                                        | MIN<br>( <u>Note 7</u> ) | TYP<br>( <u>Note 8</u> ) | MAX<br>( <u>Note 7</u> ) | UNITS     |

|----------------------------------------|----------------------|----------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|-----------|

| VCC SUPPLY CURRENT                     |                      |                                                                                        |                          |                          |                          | <u>.I</u> |

| Nominal Supply V <sub>IN</sub> Current | I <sub>Q_VIN</sub>   | $V_{IN}$ = 20V; No Load; EN1 = EN2 = high; $V_{OUT1}$ = $V_{OUT2}$ = 1.5V              |                          | 140                      |                          | mA        |

|                                        |                      | V <sub>IN1</sub> = 20V; No Load; EN1 = high, EN2 = low; V <sub>OUT1</sub> = 1.5V       |                          | 80                       |                          | mA        |

|                                        |                      | V <sub>IN2</sub> = 20V; No Load; EN1 = low, EN2 = high; V <sub>OUT2</sub> = 1.5V       |                          | 76                       |                          | mA        |

|                                        |                      | $V_{IN1}$ = 12V; No Load; EN1 = high, EN2 = high;<br>$V_{OUT1}$ = $V_{OUT2}$ = 1.5V    |                          | 159                      |                          | mA        |

|                                        |                      | $V_{IN}$ = 4.5V; No Load; EN1 = EN2 = high;<br>$V_{OUT1}$ = $V_{OUT2}$ = 1.5V          |                          | 188                      |                          | mA        |

|                                        |                      | V <sub>IN1</sub> = 4.5V; No Load; EN1 = high, EN2 = low; V <sub>OUT1</sub> = 1.5V      |                          | 102                      |                          | mA        |

|                                        |                      | V <sub>IN2</sub> = 4.5V; No Load; EN1 = low, EN2 = high; V <sub>OUT2</sub> = 1.5V      |                          | 94                       |                          | mA        |

| INTERNAL LINEAR REGULATOR (No          | <u>te 9</u> )        | 1                                                                                      |                          | 1                        | 1                        |           |

| Maximum Current                        | IPVCC                | V <sub>CC</sub> = 4V to 5.6V                                                           |                          | 250                      |                          | mA        |

| Saturated Equivalent Impedance         | R <sub>LDO</sub>     | P-Channel MOSFET (V <sub>IN</sub> = 5V)                                                |                          | 1                        |                          | Ω         |

| V <sub>CC</sub> Voltage Level          | V <sub>CC</sub>      | I <sub>VCC</sub> = 0mA                                                                 | 5.1                      | 5.4                      | 5.6                      | v         |

| POWER-ON RESET (Note 9)                | 4                    | 1                                                                                      | 1                        | I.                       | L                        | 1         |

| Rising V <sub>CC</sub> Threshold       |                      | 0°C to +75°C                                                                           |                          | 2.85                     | 2.97                     | v         |

|                                        |                      | -40°C to +85°C                                                                         |                          | 2.85                     | 3.05                     | v         |

| Falling V <sub>CC</sub> Threshold      |                      |                                                                                        |                          | 2.65                     | 2.75                     | v         |

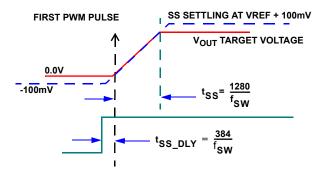

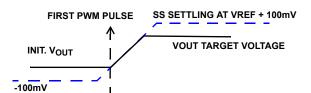

| System Soft-start Delay                | t <sub>SS_DLY</sub>  | After PLL and $V_{CC}$ PORs, and EN above their thresholds                             |                          | 384                      |                          | Cycles    |

| ENABLE (Note 9)                        | 4                    | 1                                                                                      | 1                        | I.                       | L                        | 1         |

| Turn-on Threshold Voltage              |                      |                                                                                        | 0.75                     | 0.8                      | 0.86                     | v         |

| Hysteresis Sink Current                | I <sub>EN_HYS</sub>  |                                                                                        | 23                       | 30                       | 35                       | μA        |

| Undervoltage Lockout Hysteresis        | V <sub>EN_HYS</sub>  | $V_{EN_{RTH}}$ = 10.6V; $V_{EN_{FTH}}$ = 9V, $R_{UP}$ = 53.6kΩ,<br>$R_{DOWN}$ = 5.23kΩ |                          | 1.6                      |                          | v         |

| Sink Current                           | I <sub>EN_SINK</sub> | V <sub>ENFF</sub> = 1V                                                                 | 15.4                     |                          |                          | mA        |

| Sink Impedance                         | R <sub>EN_SINK</sub> | I <sub>EN_SINK</sub> = 5mA, V <sub>ENFF</sub> = 1V                                     |                          |                          | 64                       | Ω         |

| OSCILLATOR                             |                      |                                                                                        | ·                        |                          | •                        |           |

| Oscillator Frequency                   | fosc                 | SYNC pin is open                                                                       |                          | 350                      |                          | kHz       |

| Total Variation (Note 9)               |                      | $V_{CC} = 5V; -40^{\circ}C < T_{A} < +85^{\circ}C$                                     | -9                       |                          | +9                       | %         |

**Electrical Specifications**  $T_A = +25$  °C,  $V_{IN} = 12V$ , unless otherwise noted. Boldface limits apply across the internal junction temperature range, -40 °C to +125 °C (Note 4). (Continued)

| PARAMETER                             | SYMBOL                              | TEST CONDITIONS                                                                                                                                              | MIN<br>( <u>Note 7</u> ) | TYP<br>( <u>Note 8</u> ) | MAX<br>( <u>Note 7</u> ) | UNITS             |

|---------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|-------------------|

| FREQUENCY SYNCHRONIZATION AND         | PHASE LOC                           | K LOOP (Note 9)                                                                                                                                              |                          |                          |                          |                   |

| Synchronization Frequency             |                                     | V <sub>CC</sub> = 5V                                                                                                                                         | 350                      |                          | 700                      | kHz               |

| PLL Locking Time                      |                                     | V <sub>CC</sub> = 5.4V, f <sub>SW</sub> = 500kHz                                                                                                             |                          | 130                      |                          | μs                |

| Input Signal Duty Cycle Range         |                                     |                                                                                                                                                              | 10                       |                          | 90                       | %                 |

| PWM ( <u>Note 9</u> )                 |                                     | 1                                                                                                                                                            | 1                        | 1                        | 1                        | 1                 |

| Minimum PWM OFF Time                  | t <sub>MIN_OFF</sub>                |                                                                                                                                                              | 310                      | 345                      | 410                      | ns                |

| Current Sampling Blanking Time        | t <sub>BLANKING</sub>               |                                                                                                                                                              |                          | 175                      |                          | ns                |

| OUTPUT CHARACTERISTICS                |                                     | 1                                                                                                                                                            | 1                        | 1                        | 1                        |                   |

| Output Continuous Current Range       | I <sub>OUT(DC)</sub>                | V <sub>IN</sub> = 12V, V <sub>OUT1</sub> = 1.5V                                                                                                              | 0                        |                          | 20                       | Α                 |

|                                       |                                     | V <sub>IN</sub> = 12V, V <sub>OUT2</sub> = 1.5V                                                                                                              | 0                        |                          | 20                       | Α                 |

|                                       |                                     | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V, in Parallel mode                                                                                             | 0                        |                          | 40                       | Α                 |

| Line Regulation Accuracy              | $\Delta V_{OUT} / \Delta V_{IN}$    | V <sub>IN</sub> = 4.5V to 20V                                                                                                                                |                          |                          |                          | 1                 |

|                                       |                                     | V <sub>OUT1</sub> = 1.5V, I <sub>OUT1</sub> = 0A                                                                                                             |                          | 0.0065                   |                          | %                 |

|                                       |                                     | $V_{OUT2} = 1.5V, I_{OUT2} = 0A$                                                                                                                             |                          | 0.0065                   |                          | %                 |

|                                       |                                     | V <sub>IN</sub> = 4.5V to 20V                                                                                                                                |                          |                          |                          | 1                 |

|                                       |                                     | $V_{OUT1} = 1.5V, I_{OUT1} = 20A$                                                                                                                            |                          | 0.01                     |                          | %                 |

|                                       |                                     | $V_{0UT2} = 1.5V, I_{0UT2} = 20A$                                                                                                                            |                          | 0.01                     |                          | %                 |

| Load Regulation Accuracy              | ΔV <sub>OUT</sub> /V <sub>OUT</sub> | V <sub>IN</sub> = 5V, 2x47µF ceramic capacitor and 1x330µF POSCAP                                                                                            |                          |                          |                          |                   |

|                                       |                                     | $I_{OUT1} = 0A \text{ to } 20A, V_{OUT1} = 1V$                                                                                                               |                          |                          | 1                        | %                 |

|                                       |                                     | $I_{OUT2} = 0A \text{ to } 20A, V_{OUT2} = 1V$                                                                                                               |                          |                          | 1                        | %                 |

| Output Ripple Voltage                 | ΔV <sub>OUT</sub>                   | V <sub>IN</sub> = 12V, 4x100μF +2x10μF ceramic capacitor and<br>1x330μF POSCAP                                                                               |                          |                          |                          |                   |

|                                       |                                     | I <sub>OUT1</sub> = 0A, V <sub>OUT1</sub> = 1.5V                                                                                                             |                          | 16                       |                          | mV <sub>P-P</sub> |

|                                       |                                     | I <sub>OUT2</sub> = 0A, V <sub>OUT2</sub> = 1.5V                                                                                                             |                          | 16                       |                          | mV <sub>P-P</sub> |

|                                       |                                     | I <sub>OUT1</sub> = 20A, V <sub>OUT1</sub> = 1.5V                                                                                                            |                          | 21                       |                          | mV <sub>P-P</sub> |

|                                       |                                     | I <sub>OUT2</sub> = 20A, V <sub>OUT2</sub> = 1.5V                                                                                                            |                          | 21                       |                          | mV <sub>P-P</sub> |

| DYNAMIC CHARACTERISTICS               |                                     |                                                                                                                                                              |                          | 1                        | I                        |                   |

| Voltage Change for Positive Load Step | $\Delta V_{OUT-DP}$                 | Current slew rate = $2.5A/\mu s$<br>V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V, 4x100 $\mu$ F + 2x10 $\mu$ F ceramic capacitor and 1x330 $\mu$ F POSCAP  |                          |                          |                          |                   |

|                                       |                                     | I <sub>OUT1</sub> = 0A to 10A                                                                                                                                |                          | 100                      |                          | mV <sub>P-F</sub> |

|                                       |                                     | I <sub>OUT2</sub> = 0A to 10A                                                                                                                                |                          | 100                      |                          | mV <sub>P-F</sub> |

| Voltage Change for Negative Load Step | ∆V <sub>OUT-DN</sub>                | Current slew rate = $2.5A/\mu s$<br>V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V, 4x100 $\mu$ F + 2x10 $\mu$ F ceramic capacitor, and 1x330 $\mu$ F POSCAP |                          |                          |                          |                   |

|                                       |                                     | I <sub>OUT1</sub> = 10A to 0A                                                                                                                                |                          | 80                       |                          | mV <sub>P-F</sub> |

|                                       |                                     | I <sub>OUT2</sub> = 10A to 0A                                                                                                                                |                          | 80                       |                          | mV <sub>P-F</sub> |

| REFERENCE ( <u>Note 9</u> )           | 1                                   |                                                                                                                                                              | 1                        | 1                        | L                        | 1                 |

| Reference Voltage (Include Error and  | V <sub>REF1</sub>                   | $T_A = -40$ °C to +85 °C                                                                                                                                     | 0.5958                   | 0.6                      | 0.6042                   | v                 |

| Differential Amplifier Offsets)       |                                     |                                                                                                                                                              | -0.7                     |                          | 0.7                      | %                 |

| Reference Voltage (Include Error and  | V <sub>REF2</sub>                   | $T_A = -40 \degree C$ to $+85 \degree C$                                                                                                                     | 0.5955                   | 0.6                      | 0.6057                   | v                 |

| Differential Amplifier Offsets)       |                                     |                                                                                                                                                              | -0.75                    |                          | 0.95                     | %                 |

**Electrical Specifications**  $T_A = +25$  °C,  $V_{IN} = 12V$ , unless otherwise noted. Boldface limits apply across the internal junction temperature range, -40 °C to +125 °C (Note 4). (Continued)

| PARAMETER                                                               | SYMBOL                          | TEST CONDITIONS                                                                                                  | MIN<br>( <u>Note 7</u> ) | TYP<br>( <u>Note 8</u> ) | MAX<br>( <u>Note 7</u> ) | UNITS |

|-------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|-------|

| DIFFERENTIAL AMPLIFIER ( <u>Note 9</u> )                                | 1                               |                                                                                                                  |                          |                          | I                        |       |

| DC Gain                                                                 | UG_DA                           | Unity gain amplifier                                                                                             |                          | 0                        |                          | dB    |

| Unity Gain Bandwidth                                                    | UGBW_DA                         |                                                                                                                  |                          | 5                        |                          | MHz   |

| VSEN+ Pin Sourcing Current                                              | I <sub>VSEN+</sub>              |                                                                                                                  | 0.2                      | 1                        | 2.5                      | μA    |

| Maximum Source Current for Current<br>Sharing                           | IVSEN1-                         | VSEN1- Source Current for Current Sharing when parallel multiple modules, each of which has its own voltage loop |                          | 350                      |                          | μA    |

| Input Impedance                                                         | R <sub>VSEN+_to</sub><br>_VSEN- | V <sub>VSEN+</sub> /I <sub>VSEN+</sub> , V <sub>VSEN+</sub> = 0.6V                                               |                          | -600                     |                          | kΩ    |

| Output Voltage Swing                                                    |                                 |                                                                                                                  | 0                        |                          | V <sub>CC</sub> - 1.8    | v     |

| Input Common Mode Range                                                 |                                 |                                                                                                                  | -0.2                     |                          | V <sub>CC</sub> - 1.8    | v     |

| Disable Threshold                                                       | V <sub>VSEN-</sub>              | V <sub>MON1,2</sub> = tri-state                                                                                  |                          | V <sub>CC</sub> - 0.4    |                          | v     |

| OVERCURRENT PROTECTION (Note 9)                                         | 1                               |                                                                                                                  |                          |                          | L                        |       |

| Channel Overcurrent Limit                                               | I <sub>limit1</sub>             | V <sub>IN</sub> = 12V, V <sub>OUT1</sub> = 1.5V, R <sub>SYNC</sub> = 768k                                        |                          | 24.5                     |                          | Α     |

|                                                                         | I <sub>limit2</sub>             | V <sub>IN</sub> = 12V, V <sub>OUT2</sub> = 1.5V, R <sub>SYNC</sub> = 768k                                        |                          | 24                       |                          | Α     |

| Share Pin OC Threshold                                                  | V <sub>OC_SET</sub>             | V <sub>CC</sub> = 5V (comparator offset included)                                                                | 1.16                     | 1.20                     | 1.22                     | v     |

| CURRENT SHARE                                                           |                                 |                                                                                                                  |                          |                          | L                        |       |

| Current Share Accuracy                                                  | ∆I/IOUT                         | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V<br>I <sub>OUT</sub> = 40A, VSEN2- = high                          |                          | ±10                      |                          | %     |

| POWER-GOOD MONITOR (Note 9)                                             | 1                               |                                                                                                                  |                          | 1                        | 1                        |       |

| Undervoltage Falling Trip Point                                         | V <sub>UVF</sub>                | Percentage below reference point                                                                                 | -15                      | -13                      | -11                      | %     |

| Undervoltage Rising Hysteresis                                          | V <sub>UVR_HYS</sub>            | Percentage above UV trip point                                                                                   |                          | 4                        |                          | %     |

| Overvoltage Rising Trip Point                                           | V <sub>OVR</sub>                | Percentage above reference point                                                                                 | 11                       | 13                       | 15                       | %     |

| Overvoltage Falling Hysteresis                                          | V <sub>OVF_HYS</sub>            | Percentage below OV trip point                                                                                   |                          | 4                        |                          | %     |

| PGOOD Low Output Voltage                                                |                                 | I <sub>PGOOD</sub> = 2mA                                                                                         |                          |                          | 0.35                     | v     |

| Sinking Impedance                                                       |                                 | I <sub>PG00D</sub> = 2mA                                                                                         |                          |                          | 70                       | Ω     |

| Maximum Sinking Current                                                 |                                 | V <sub>PGOOD</sub> < 0.8V                                                                                        |                          | 10                       |                          | mA    |

| OVERVOLTAGE PROTECTION (Note 9)                                         | 1                               |                                                                                                                  |                          | 1                        | I                        |       |

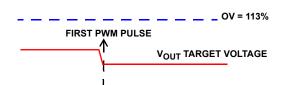

| OV Latching-up Trip Point                                               |                                 | EN/FF = UGATE = LATCH Low, LGATE = High                                                                          | 118                      | 120                      | 122                      | %     |

| OV Non-Latching-up Trip Point                                           |                                 | EN = Low, UGATE = Low, LGATE = High                                                                              |                          | 113                      |                          | %     |

| LGATE Release Trip Point                                                |                                 | EN = Low/HIGH, UGATE = Low, LGATE = Low                                                                          |                          | 87                       |                          | %     |

| OVER-TEMPERATURE PROTECTION (                                           | lote 9)                         |                                                                                                                  |                          |                          |                          |       |

| Over-Temperature Trip (Controller<br>Junction Temperature)              |                                 |                                                                                                                  |                          | 150                      |                          | °C    |

| Over-Temperature Release Threshold<br>(Controller Junction Temperature) |                                 |                                                                                                                  |                          | 125                      |                          | °C    |

NOTES:

7. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

8. Parameters with TYP limits are not production tested, unless otherwise specified.

9. Parameters are 100% tested for internal IC prior to module assembly.

### **Typical Performance Characteristics**

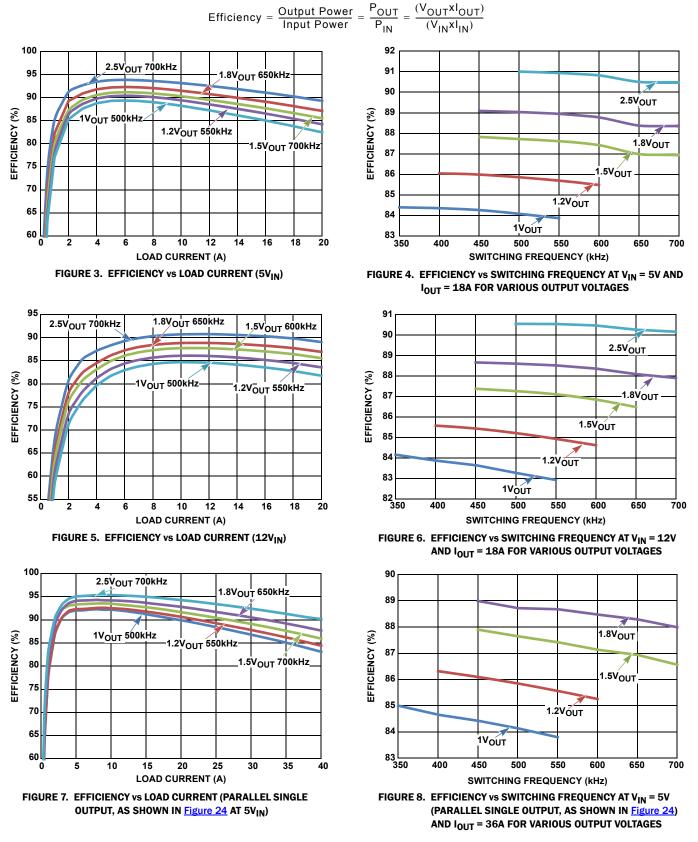

**Efficiency Performance**  $T_A = +25$ °C, if not specified, as shown in Figure 23 with 2nd phase disabled. The efficiency equation is as follows:

### ISL8240M

#### 100 92 91 95 2.5V<sub>OUT</sub> 700kHz 1.8V<sub>OUT</sub> 650kHz 90 2.5V<sub>OUT</sub> 90 89 (%) EFFICIENCY (%) 85 EFFICIENCY 1.2V<sub>OUT</sub> 550kHz 88 1.8V<sub>OUT</sub> V<sub>OUT</sub> 500kHz 80 1.5V<sub>OUT</sub> 700kHz 87 75 86 5VOUT 70 85 1.2V<sub>OUT</sub> 65 84 1Vout 60 83 5 10 15 20 25 30 35 40 350 450 550 400 500 600 650 700 0 LOAD CURRENT (A) SWITCHING FREQUENCY (kHz) FIGURE 9. EFFICIENCY vs LOAD CURRENT (PARALLEL SINGLE FIGURE 10. EFFICIENCY vs SWITCHING FREQUENCY AT $V_{IN} = 12V$ (PARALLEL SINGLE OUTPUT, AS SHOWN IN Figure 24 AT OUTPUT, AS SHOWN IN Figure 24 AT 12VIN) 12VIN) AND IOUT = 18A FOR VARIOUS OUTPUT VOLTAGES

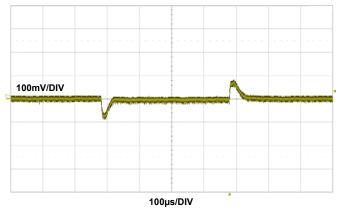

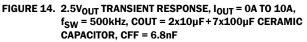

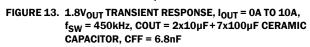

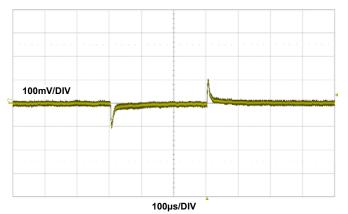

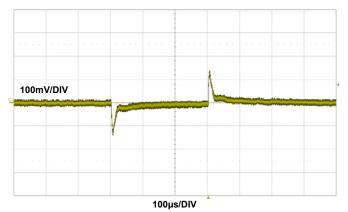

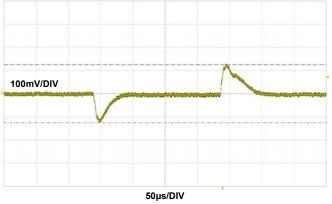

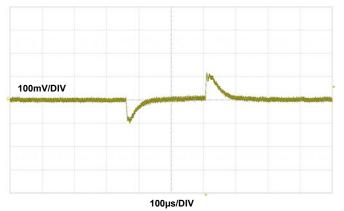

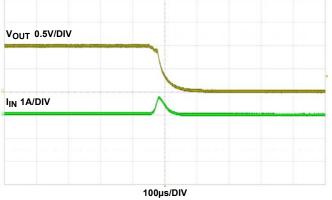

**Transient Response Performance**  $V_{IN} = 12V$  current slew rate = 10A/µs.  $T_A = +25$ °C, if not specified, as shown in Figure 23 with 2nd phase disabled.

**Typical Performance Characteristics** (Continued)

FIGURE 11. 1V<sub>OUT</sub> TRANSIENT RESPONSE, I<sub>OUT</sub> = 0A TO 10A,  $f_{SW} = 350$ kHz, COUT = 2x10µF+7x100µF CERAMIC CAPACITOR, CFF = 6.8nF

FIGURE 12. 1.5V<sub>OUT</sub> TRANSIENT RESPONSE, I<sub>OUT</sub> = 0A TO 10A,  $f_{SW} = 400$ kHz, COUT = 2x10µF+7x100µF CERAMIC CAPACITOR, CFF = 6.8nF

100mV/DIV

100us/DIV

### Typical Performance Characteristics (Continued)

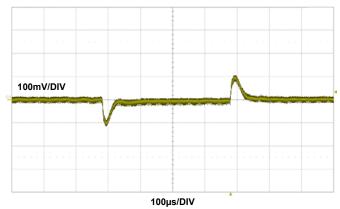

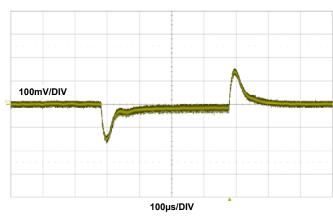

**Transient Response Performance**  $V_{IN} = 12V$  current slew rate =  $10A/\mu s$ .  $T_A = +25°C$ , if not specified, as shown in Figure 23 with 2nd phase disabled. (Continued)

FIGURE 15.  $1V_{OUT}$  DUAL PHASE SINGLE OUTPUT TRANSIENT RESPONSE, I<sub>OUT</sub> = 0A TO 20A, f<sub>SW</sub> = 350kHz, COUT = 330µF POSCAP+10µF+5x100µF CERAMIC CAPACITOR

FIGURE 16. 1.5V<sub>OUT</sub> DUAL PHASE SINGLE OUTPUT TRANSIENT RESPONSE, I<sub>OUT</sub> = 0A TO 20A, f<sub>SW</sub> = 400kHz, COUT =  $330\mu$ F POSCAP+ $10\mu$ F+ $5x100\mu$ F CERAMIC CAPACITOR

FIGURE 17. 0.9V<sub>OUT</sub> FOUR PHASE SINGLE OUTPUT TRANSIENT RESPONSE,  $I_{OUT}$  = 0A TO 40A,  $f_{SW}$  = 350kHz, COUT = 6x330µF POSCAP+7x47µF+4x100µF CERAMIC CAPACITOR

FIGURE 18.  $1V_{OUT}$  SIX PHASE SINGLE OUTPUT TRANSIENT RESPONSE,  $I_{OUT}$  = 0A TO 60A,  $f_{SW}$  = 350kHz, COUT = 6x330µF POSCAP+7x47µF+6x100µF CERAMIC CAPACITOR

### Typical Performance Characteristics (Continued)

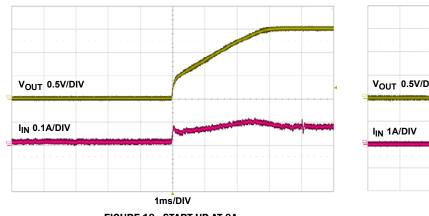

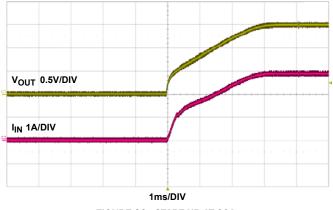

**Start-up and Short Circuit Performance**  $V_{IN} = 12V$ ,  $V_{OUT} = 1.5V$ , CIN =  $1x330\mu$ F,  $3x22\mu$ F/Ceramic, COUT =  $330\mu$ F POSCAP+ $1x10\mu$ F+ $4x100\mu$ F Ceramic.  $T_A = +25$ °C, if not specified, as shown in Figure 23 with 2nd phase disabled.

FIGURE 19. START-UP AT 0A

FIGURE 20. START-UP AT 20A

FIGURE 21. SHORT CIRCUIT AT 0A

FIGURE 22. SHORT CIRCUIT AT 20A

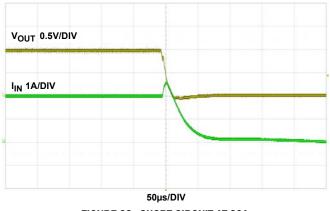

SEE <u>"LAYOUT GUIDE" ON PAGE 25</u> FOR SHORTING SGND TO PGND

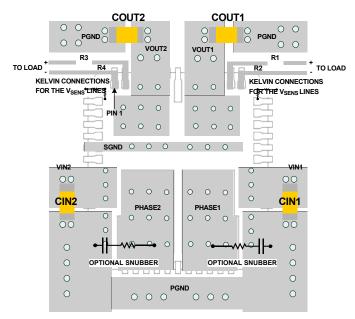

FIGURE 24. PARALLEL USE FOR SINGLE 1.2V/40A OUTPUT

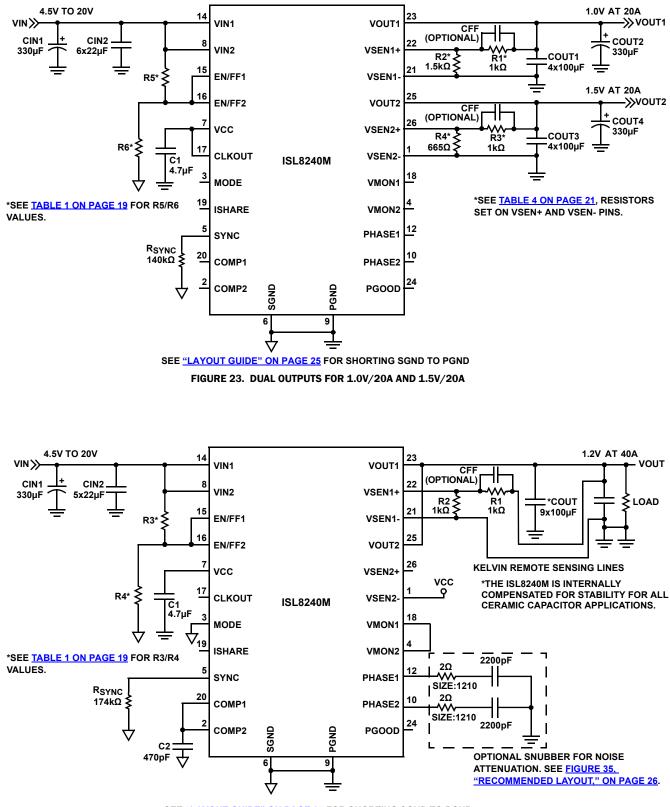

FIGURE 25. DDR/TRACKING USE

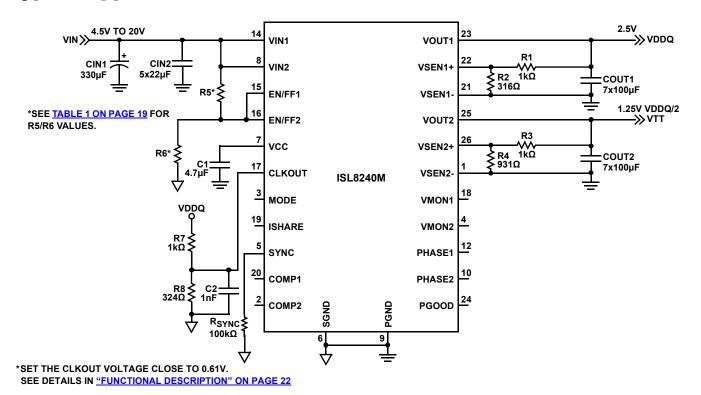

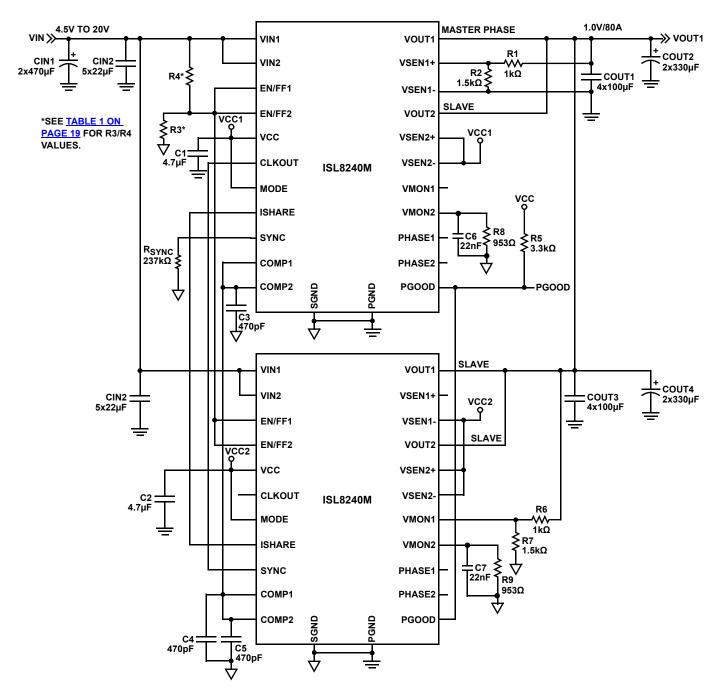

FIGURE 26. 4-PHASE PARALLELED AT 1.0V/80A WITH 90° INTERLEAVING

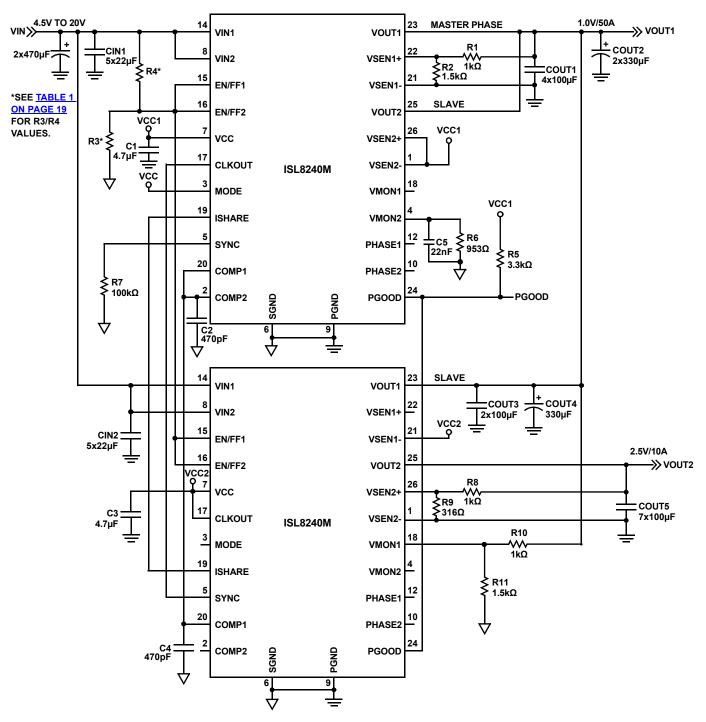

FIGURE 27. 3-PHASE PARALLELED AT 1.0V/50A AND 1-PHASE AT 2.5V/10A OUTPUT WITH 90° INTERLEAVING

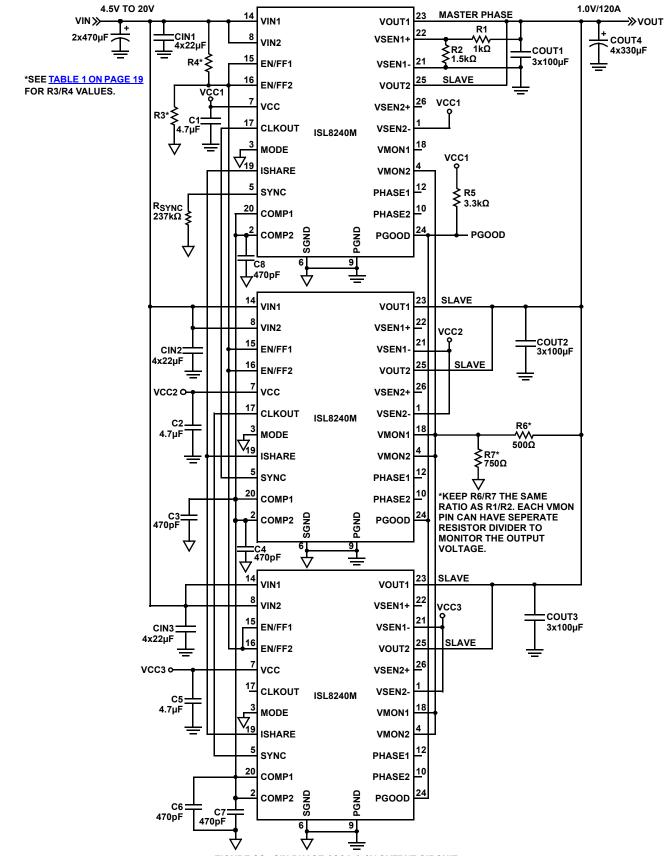

FIGURE 28. SIX-PHASE 120A 1.0V OUTPUT CIRCUIT

### **ISL8240M**

| CASE | V <sub>IN</sub><br>(V) | V <sub>OUT</sub><br>(V) | R2 or R4<br>(Ω) | CIN1<br>(BULK) (µF)<br>( <u>Note 10</u> ) | CIN2<br>(CERAMIC)<br>(µF) | COUT1<br>(CERAMIC)<br>(µF) | COUT2<br>(BULK) | CFF<br>(nF) | EN/FF (kΩ)<br>R5/R6<br>( <u>Note 11</u> ) | FREQ.<br>(kHz) | R <sub>SYNC</sub><br>(kΩ) | LOAD<br>(A)<br>( <u>Note 12</u> ) |

|------|------------------------|-------------------------|-----------------|-------------------------------------------|---------------------------|----------------------------|-----------------|-------------|-------------------------------------------|----------------|---------------------------|-----------------------------------|

| 1    | 5                      | 1                       | 1.5k            | 1x330                                     | 1x100                     | 4x100                      | 1x330µF         | None        | 6.04/3.01                                 | 500            | 237                       | 20                                |

| 2    | 5                      | 1                       | 1.5k            | 1x330                                     | 1x100                     | 7x100                      | None            | 6.8         | 6.04/3.01                                 | 500            | 237                       | 20                                |

| 3    | 12                     | 1                       | 1.5k            | 1x330                                     | 3x22                      | 4x100                      | 1x330µF         | None        | 6.04/1.50                                 | 500            | 237                       | 20                                |

| 4    | 12                     | 1                       | 1.5k            | 1x330                                     | 3x22                      | 7x100                      | None            | 6.8         | 6.04/1.50                                 | 500            | 237                       | 20                                |

| 5    | 5                      | 1.2                     | 1.0k            | 1x330                                     | 1x100                     | 4x100                      | 1x330µF         | None        | 6.04/3.01                                 | 550            | 174                       | 20                                |

| 6    | 5                      | 1.2                     | 1.0k            | 1x330                                     | 1x100                     | 7x100                      | None            | 6.8         | 6.04/3.01                                 | 550            | 174                       | 20                                |

| 7    | 12                     | 1.2                     | 1.0k            | 1x330                                     | 3x22                      | 4x100                      | 1x330µF         | None        | 6.04/1.50                                 | 550            | 174                       | 20                                |

| 8    | 12                     | 1.2                     | 1.0k            | 1x330                                     | 3x22                      | 7x100                      | None            | 6.8         | 6.04/1.50                                 | 550            | 174                       | 20                                |

| 9    | 20                     | 1.2                     | 1.0k            | 1x330                                     | 3x22                      | 4x100                      | 1x330µF         | None        | 6.04/1.50                                 | 550            | 174                       | 19                                |

| 10   | 20                     | 1.2                     | 1.0k            | 1x330                                     | 3x22                      | 7x100                      | None            | 6.8         | 6.04/1.50                                 | 550            | 174                       | 19                                |

| 11   | 5                      | 1.5                     | 665             | 1x330                                     | 1x100                     | 4x100                      | 1x330µF         | None        | 6.04/3.01                                 | 700            | 100                       | 18                                |

| 12   | 5                      | 1.5                     | 665             | 1x330                                     | 1x100                     | 7x100                      | None            | 6.8         | 6.04/3.01                                 | 700            | 100                       | 18                                |

| 13   | 12                     | 1.5                     | 665             | 1x330                                     | 3x22                      | 4x100                      | 1x330µF         | None        | 6.04/1.50                                 | 600            | 140                       | 19                                |

| 14   | 12                     | 1.5                     | 665             | 1x330                                     | 3x22                      | 7x100                      | None            | 6.8         | 6.04/1.50                                 | 600            | 140                       | 19                                |

| 15   | 20                     | 1.5                     | 665             | 1x330                                     | 3x22                      | 4x100                      | 1x330µF         | None        | 6.04/1.50                                 | 600            | 140                       | 18                                |

| 16   | 20                     | 1.5                     | 665             | 1x330                                     | 3x22                      | 7x100                      | None            | 6.8         | 6.04/1.50                                 | 600            | 140                       | 18                                |

| 17   | 5                      | 2.5                     | 316             | 1x330                                     | 1x100                     | 4x100                      | 1x330µF         | None        | 6.04/3.01                                 | 700            | 100                       | 18                                |

| 18   | 5                      | 2.5                     | 316             | 1x330                                     | 1x100                     | 7x100                      | None            | 6.8         | 6.04/3.01                                 | 700            | 100                       | 18                                |

| 19   | 12                     | 2.5                     | 316             | 1x330                                     | 3x22                      | 4x100                      | 1x330µF         | None        | 6.04/1.50                                 | 700            | 100                       | 18                                |

| 20   | 12                     | 2.5                     | 316             | 1x330                                     | 3x22                      | 7x100                      | None            | 6.8         | 6.04/1.50                                 | 700            | 100                       | 18                                |

| 21   | 20                     | 2.5                     | 316             | 1x330                                     | 3x22                      | 4x100                      | 1x330µF         | None        | 6.04/1.50                                 | 700            | 100                       | 16                                |

| 22   | 20                     | 2.5                     | 316             | 1x330                                     | 3x22                      | 7x100                      | None            | 6.8         | 6.04/1.50                                 | 700            | 100                       | 16                                |

TABLE 1. ISL8240M DESIGN GUIDE MATRIX (REFER TO Figure 23)

NOTES:

10. CIN bulk capacitor is optional only for decoupling noise due to the long input cable. CIN2 and COUT1 ceramic capacitors are listed for one phase only. Please increase the capacitor quantity for dual-phase operations.

11. EN/FF resistor divider is tied directly to VIN. The resistors listed here are for two channels' EN/FF pins tied together. If the separate resistor divider is used for each channel, the resistor value needs to be doubled.

12. MAX load current listed in the table is for conditions at +25°C and no air flow on a typical Intersil 4-layer evaluation board.

| VENDOR                           | VALUE             | PART NUMBER        |  |  |  |  |  |

|----------------------------------|-------------------|--------------------|--|--|--|--|--|

| TDK, Input and Output Ceramic    | 100µF, 6.3V, 1210 | C3225X5R0J107M     |  |  |  |  |  |

| Murata, Input and Output Ceramic | 100µF, 6.3V, 1210 | GRM32ER60J107M     |  |  |  |  |  |

| AVX, Input and Output Ceramic    | 100µF, 6.3V, 1210 | 12106D107MAT2A     |  |  |  |  |  |

| Murata, Input Ceramic            | 22µF, 25V, 1210   | GRM32ER61E226KE15L |  |  |  |  |  |

| Taiyo Yuden, Input Ceramic       | 22µF, 25V, 1210   | TMK325BJ226MM-T    |  |  |  |  |  |

| AVX, Input Ceramic               | 22µF, 25V, 1210   | 12103D226KAT2A     |  |  |  |  |  |

| Panasonic POSCAP, Output Bulk    | 330µF, 6.3V       | 6TPF330M9L         |  |  |  |  |  |

| Panasonic SMT, Input Bulk        | 330µF, 25V        | EEVHA1E331UP       |  |  |  |  |  |

| 1ST MODULE (I = INPUT; 0 = OUTPUT; I/O = INPUT AND OUTPUT, BIDIRECTION) MODES OF OPERATIO |                                                                                 |                |                         |                 |                 | OPERATION                                       |                                          |                                                    |                                                                          |                                                   |                                                   |                                                     |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------|-------------------------|-----------------|-----------------|-------------------------------------------------|------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|

| MODE                                                                                      | EN1/FF1<br>(l)                                                                  | EN2/FF2<br>(l) | VSEN2-<br>(I)           | MODE<br>(I)     | VSEN2+<br>(I)   | CLKOUT/REFIN<br>WRT 1 <sup>ST</sup><br>(I OR 0) | VMON2<br>( <u>Note 14</u> )              | VMON1<br>OF 2 <sup>ND</sup><br>MODULE<br>(Note 14) | 2 <sup>ND</sup> CHANNEL<br>WRT 1 <sup>ST</sup> (0)<br>( <u>Note 13</u> ) | OPERATION<br>MODE<br>OF 2 <sup>ND</sup><br>MODULE | OPERATION<br>MODE<br>OF 3 <sup>RD</sup><br>MODULE | OUTPUT<br>(see<br>Description for<br>details)       |