# KSZ8041NL/RNL

10Base-T/100Base-TX Physical Layer Transceiver

## **Revision 1.5**

## **General Description**

The KSZ8041NL is a single supply 10Base-T/100Base-TX physical layer transceiver, which provides MII/RMII interfaces to transmit and receive data. A unique mixed signal design extends signaling distance while reducing power consumption.

HP Auto MDI/MDI-X provides the most robust solution for eliminating the need to differentiate between crossover and straight-through cables.

The KSZ8041NL represents a new level of features and performance and is an ideal choice of physical layer transceiver for 10Base-T/100Base-TX applications.

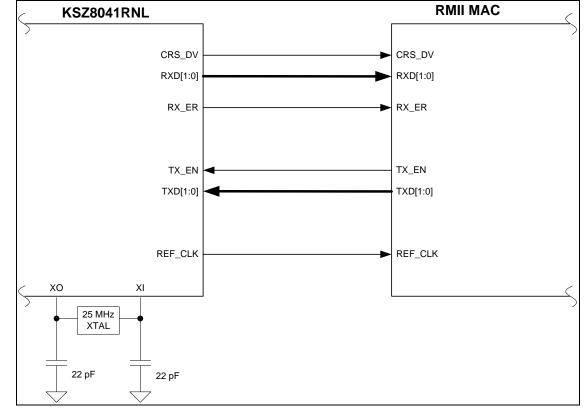

The KSZ8041RNL is an enhanced RMII version of the KSZ8041NL that does not require a 50MHz system clock. It uses a 25MHz crystal for its input reference clock and outputs a 50MHz RMII reference clock to the MAC.

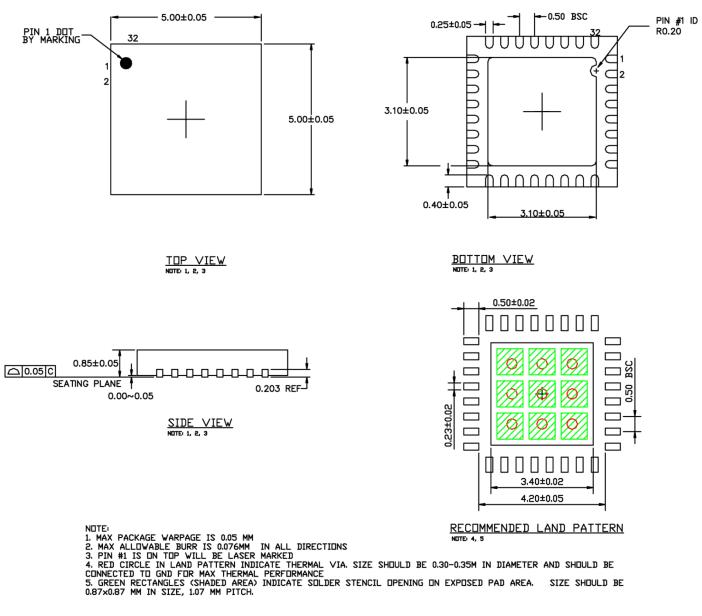

The KSZ8041NL and KSZ8041RNL are available in 32pin, lead-free QFN packages (see *Ordering Information*).

Datasheets and support documentation are available on Micrel's web site at: <u>www.micrel.com</u>.

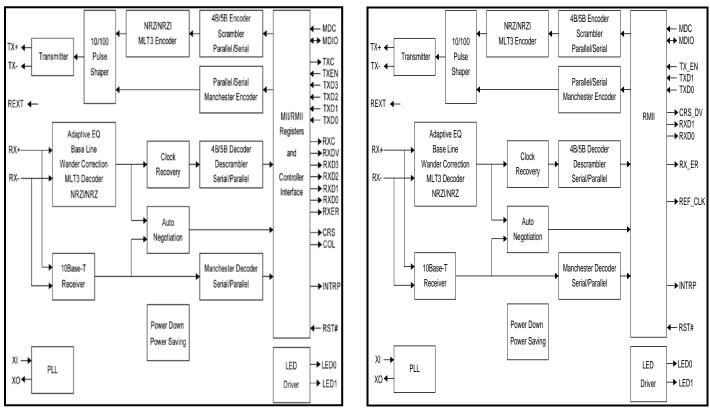

## **Functional Diagram**

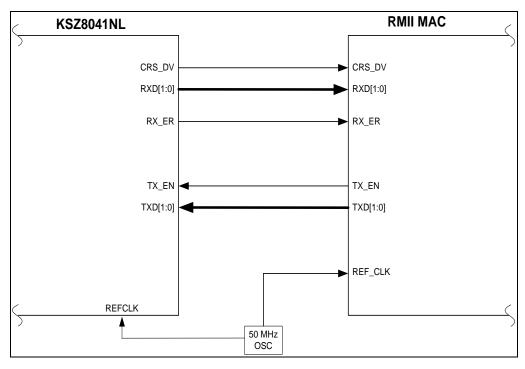

KSZ8041NL

KSZ8041RNL

## Features

- Single-chip 10Base-T/100Base-TX physical layer solution

- Fully compliant to IEEE 802.3u standard

- Low power CMOS design, power consumption of <180mW</li>

- HP auto MDI/MDI-X for reliable detection and correction for straight-through and crossover cables with disable and enable option

- Robust operation over standard cables

- Power down and power saving modes

- MII interface support (KSZ8041NL only)

- RMII interface support with external 50MHz system clock (KSZ8041NL only)

- RMII interface support with 25MHz crystal/clock input and 50MHz reference clock output to MAC (KSZ8041RNL only)

- MIIM (MDC/MDIO) management bus to 6.25MHz for rapid PHY register configuration

- Interrupt pin option

- Programmable LED outputs for link, activity and speed

- ESD rating (6kV)

- Single power supply (3.3V)

- Built-in 1.8V regulator for core

- Available in 32-pin 5mm × 5mm QFN package

# Applications

- Printer

- LOM

- Game console

- IPTV

- IP phone

- IP set-top box

# **Ordering Information**

For the device marking (second column in the Ordering Information table), the fifth character of line 3 indicates whether the device has gold wire bonding or silver wire bonding, as follows:

- Gold wire bonding: The letter "S" is not present as the fifth character of line 3.

- Silver wire bonding: The letter "S" is present as the fifth character of line 3.

For line three, the presence or non-presence of the letter "S" is preceded by YYWW, indicating the last two digits of the year and the two digits work week for the chip date code, and is followed by xxx, indicating the chip revision and assembly site.

| Part Number                 | Device<br>Marking                | Package    | Temperature<br>Range | Wire<br>Bonding | Description                                                                                                                         |

|-----------------------------|----------------------------------|------------|----------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|

| KSZ8041NL                   | KSZ8041NL<br>YYWWxxx             | 32-Pin QFN | 0°C to 70°C          | Gold            | MII, Commercial Temperature, Gold<br>Wire Bonding, 32-Pin QFN, Pb-Free                                                              |

| SPNZ801162 <sup>(1)</sup>   | KSZ8041NL<br>YYWW <b>S</b> xxx   | 32-Pin QFN | 0°C to 70°C          | Silver          | MII, Commercial Temperature, Silver<br>Wire Bonding, 32-Pin QFN, Pb-Free                                                            |

| KSZ8041NLI                  | KSZ8041NLI<br>YYWWxxx            | 32-Pin QFN | –40°C to 85°C        | Gold            | MII, Industrial Temperature, Gold Wire<br>Bonding, 32-Pin QFN, Pb-Free                                                              |

| SPNY801162 <sup>(1)</sup>   | KSZ8041NLI<br>YYWW <b>S</b> xxx  | 32-Pin QFN | –40°C to 85°C        | Silver          | MII, Industrial Temperature, Silver Wire<br>Bonding, 32-Pin QFN, Pb-Free                                                            |

| KSZ8041NL AM <sup>(1)</sup> | KSZ8041NL<br>AM<br>YYWWxxx       | 32-Pin QFN | –40°C to 85°C        | Gold            | MII, Industrial Temperature, Gold Wire<br>Bonding, 32-Pin QFN, Pb-Free,<br>Automotive Qualified Device.                             |

| KSZ8041RNLU <sup>(1)</sup>  | KSZ8041<br>RNLU<br>YYWWxxx       | 32-Pin QFN | -40°C to 85°C        | Gold            | RMII with 50MHz clock output, Industrial<br>Temperature, Gold Wire Bonding, 32-Pin<br>QFN, Pb-Free, Automotive Qualified<br>Device. |

| KSZ8041RNL                  | KSZ8041RNL<br>YYWWxxx            | 32-Pin QFN | 0°C to 70°C          | Gold            | RMII with 50MHz clock output,<br>Commercial Temperature, Gold Wire<br>Bonding, 32-Pin QFN, Pb-Free                                  |

| SPNZ801164 <sup>(1)</sup>   | KSZ8041RNL<br>YYWW <b>S</b> xxx  | 32-Pin QFN | 0°C to 70°C          | Silver          | RMII with 50MHz clock output,<br>Commercial Temperature, Silver Wire<br>Bonding, 32-Pin QFN, Pb-Free                                |

| KSZ8041RNLI                 | KSZ8041RNLI<br>YYWWxxx           | 32-Pin QFN | –40°C to 85°C        | Gold            | RMII with 50MHz clock output, Industrial<br>Temperature, Gold Wire Bonding, 32-Pin<br>QFN, Pb-Free                                  |

| SPNY801164 <sup>(1)</sup>   | KSZ8041RNLI<br>YYWW <b>S</b> xxx | 32-Pin QFN | –40°C to 85°C        | Silver          | RMII with 50MHz clock output, Industrial<br>Temperature, Silver Wire Bonding, 32-<br>Pin QFN, Pb-Free                               |

Note:

1. Contact factory for availability.

# **Revision History**

| Revision | Date     | Summary of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 10/13/06 | Data sheet created.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.1      | 4/27/07  | Added maximum MDC clock speed.<br>Added 40K ±30% to Note 1 of Pin Description and Strapping Options tables for internal pull-ups/pull-<br>downs.<br>Changed Model Number in Register 3h – PHY Identifier 2.<br>Changed polarity (swapped definition) of DUPLEX strapping pin.<br>Removed DUPLEX strapping pin update to Register 4h – Auto-Negotiation Advertisement bits [8, 6].<br>Set "Disable power saving" as the default for Register 1Fh bit [10].<br>Corrected LED1 (pin 31) definition for Activity in LED mode 01.<br>Added Symbol Error to MII/RMII Receive Error description and Register 15h – RXER Counter.<br>Added a 100pF capacitor on REXT (pin 10) in Pin Description table.                                                                                                                                                           |

| 1.2      | 7/18/08  | Added Automotive Qualified part number to Ordering Information.<br>Added maximum case temperature.<br>Added thermal resistance ( $\theta_{JC}$ ).<br>Added chip maximum current consumption.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.3      | 12/11/09 | Added Automotive Qualified part number, KSZ8041NL EAM, to Ordering Information.<br>Changed MDIO hold time (min) from 10ns to 4ns.<br>Added LED drive current.<br>Renamed Register 3h bits [3:0] to "manufacturer's revision number" and changed default value to<br>"Indicates silicon revision."<br>Updated RMII output delay for CRSDV and RXD[1:0] output pins.<br>Added support for Asymmetric PAUSE in register 4h bit [11].<br>Added control bits for 100Base-TX preamble restore (register 14h bit [7]) and 10Base-T preamble restore<br>(register 14h bit [6]).<br>Changed strapping pin definition for CONFIG[2:0] = 100 from "PCS Loopback" to "MII 100Mbps Preamble<br>Restore."<br>Corrected MII timing for t <sub>RLAT</sub> , t <sub>CRS1</sub> , t <sub>CRS2</sub> .<br>Added KSZ8041RNL device and updated entire data sheet accordingly. |

| 1.4      | 1/19/10  | Removed part number (KSZ8041NL EAM) from Ordering Information.<br>Removed chip maximum current consumption.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.5      | 2/2/15   | Added automotive qualified part number, KSZ8041RNLU.<br>Changed VDDPLL_1.8 (Pin 2) decoupling capacitor value from 10µF to 1.0µF.<br>Specified minimum 250µs rise time for 3.3V input supply voltages (V <sub>DDI0_3.3</sub> , V <sub>DDA_3.3</sub> ).<br>Add the part numbers of the silver wire bonding in <i>Ordering Information</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# Contents

| List of Figures                                              |    |

|--------------------------------------------------------------|----|

| List of Tables                                               |    |

| Pin Configuration – KSZ8041NL                                |    |

| Pin Description – KSZ8041NL<br>Strapping Options – KSZ8041NL |    |

| Pin Configuration – KSZ8041RNL                               |    |

| Pin Description – KSZ8041RNL                                 |    |

| Strapping Options – KSZ8041RNL                               |    |

| Functional Description 100Base-TX Transmit                   |    |

| 100Base-TX Receive                                           |    |

| PLL Clock Synthesizer                                        |    |

| Scrambler/De-Scrambler (100Base-TX only)                     |    |

| 10Base-T Transmit                                            |    |

| 10Base-T Receive                                             | 21 |

| SQE and Jabber Function (10Base-T only)                      | 21 |

| Auto-Negotiation                                             | 21 |

| MII Management (MIIM) Interface                              | 23 |

| Interrupt (INTRP)                                            | 23 |

| MII Data Interface (KSZ8041NL only)                          | 23 |

| MII Signal Definition (KSZ8041NL only)                       | 24 |

| Transmit Clock (TXC)                                         | 24 |

| Transmit Enable (TXEN)                                       |    |

| Transmit Data [3:0] (TXD[3:0])                               |    |

| Receive Clock (RXC)                                          |    |

| Receive Data Valid (RXDV)                                    |    |

| Receive Data [3:0] (RXD[3:0])                                |    |

| Receive Error (RXER)                                         |    |

| Carrier Sense (CRS)                                          |    |

| Collision (COL)                                              | 25 |

| Reduced MII (RMII) Data Interface                            |    |

| RMII Signal Definition                                       |    |

| Reference Clock (REF_CLK)                                    |    |

| Transmit Enable (TX_EN)                                      |    |

| Transmit Data [1:0] (TXD[1:0])                               |    |

| Carrier Sense/Receive Data Valid (CRS_DV)                    | 27 |

| Receive Data [1:0] (RXD[1:0])                                | 27 |

| Receive Error (RX_ER)                                        | 27 |

| Collision Detection                                          | 27 |

| RMII Signal Diagram                                 | 27 |

|-----------------------------------------------------|----|

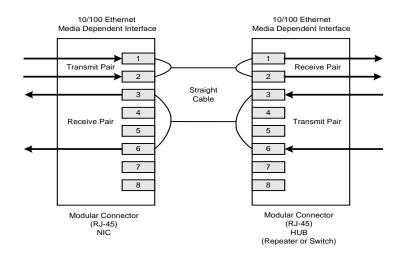

| Straight Cable                                      |    |

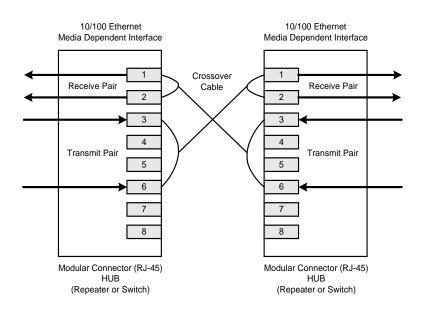

| Crossover Cable                                     |    |

| Power Management                                    |    |

| Power Saving Mode                                   |    |

| Power-Down Mode                                     |    |

| Reference Clock Connection Options                  |    |

| Reference Circuit for Power and Ground Connections  |    |

| Register Map                                        |    |

| Register Description                                |    |

| Absolute Maximum Ratings                            |    |

| Operating Ratings                                   |    |

| Electrical Characteristics                          |    |

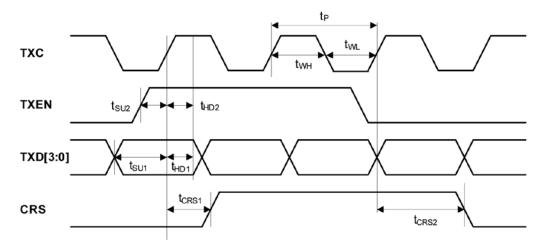

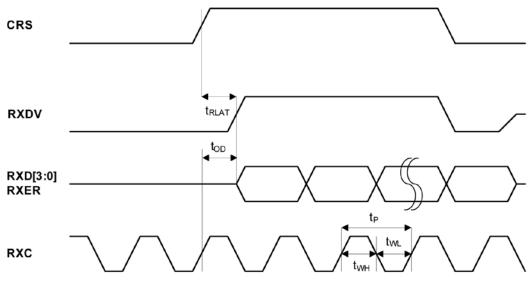

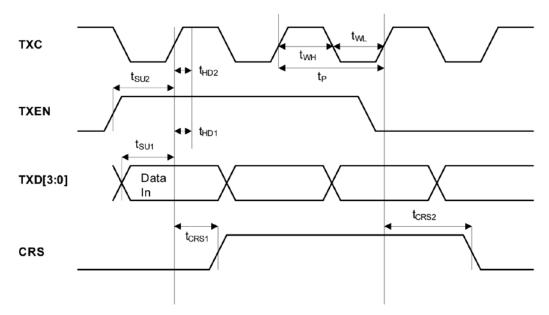

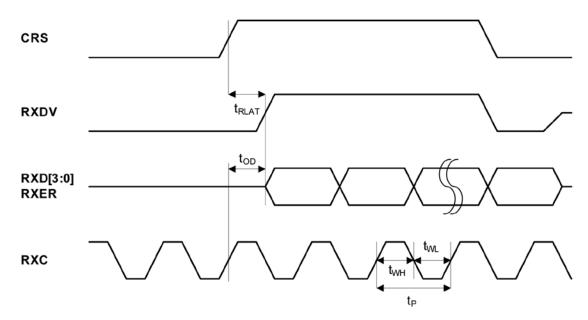

| Timing Diagrams<br>MII Transmit Timing (10Base-T)   |    |

|                                                     |    |

| MII Receive Timing (10Base-T)                       |    |

| MII Transmit Timing (100Base-TX)                    |    |

| MII Receive Timing (100Base-TX)                     |    |

| RMII Timing                                         |    |

| Auto-Negotiation Timing                             |    |

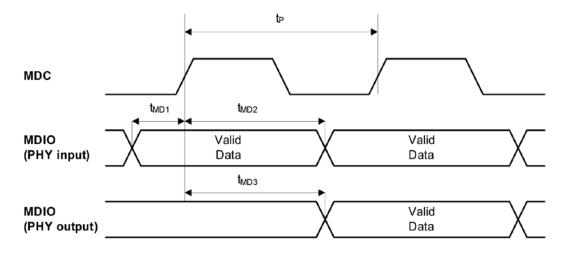

| MDC/MDIO Timing                                     | 51 |

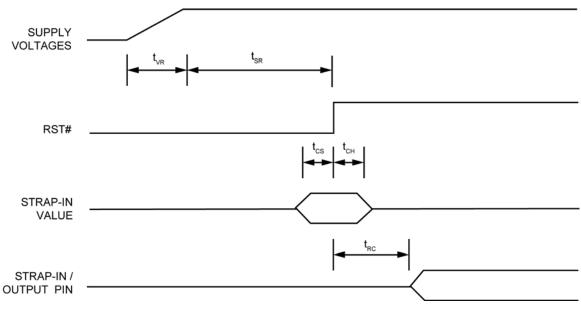

| Power-Up/Reset Timing                               |    |

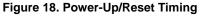

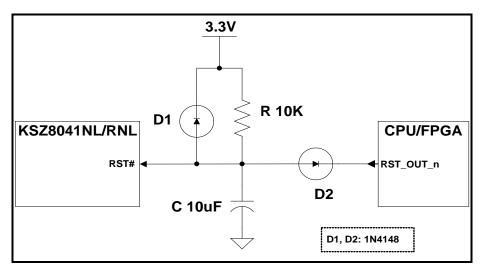

| Reset Circuit                                       |    |

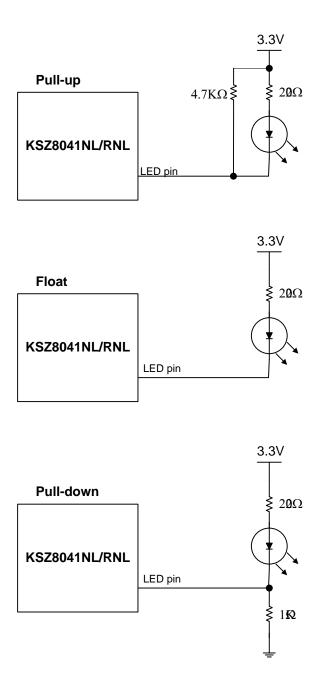

| Reference Circuits for LED Strapping Pins           |    |

| Selection of Isolation Transformer                  |    |

| Selection of Reference Crystal                      |    |

| Package Information and Recommended Landing Pattern |    |

# List of Figures

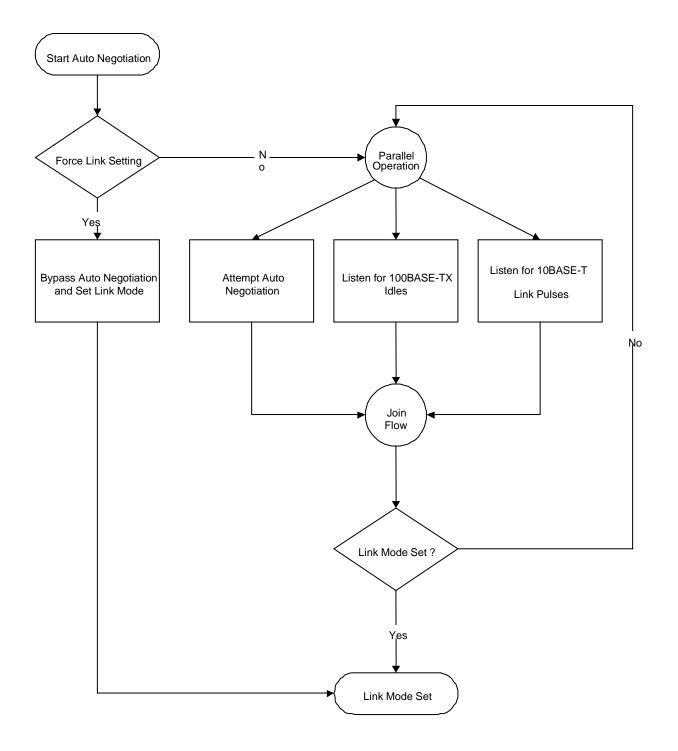

| Figure 1.  | Auto-Negotiation Flow Chart                                          | 22 |

|------------|----------------------------------------------------------------------|----|

| Figure 2.  | KSZ8041NL RMII Interface                                             | 27 |

| Figure 3.  | KSZ8041RNL RMII Interface                                            | 28 |

|            | Typical Straight Cable Connection                                    |    |

| Figure 5.  | Typical Crossover Cable Connection                                   | 29 |

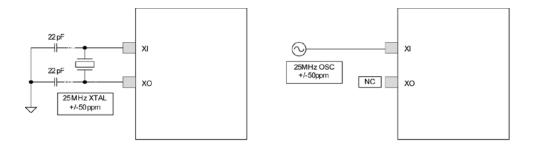

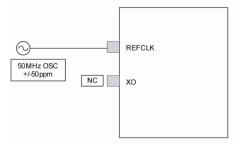

| Figure 6.  | 25MHz Crystal/Oscillator Reference Clock                             | 30 |

| Figure 7.  | 50MHz Oscillator Reference Clock fo KSZ8041NL RMII Mode              | 30 |

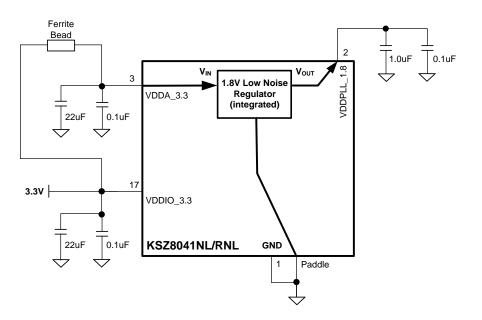

| Figure 8.  | KSZ8041NL/RNL Power and Ground Connections                           | 31 |

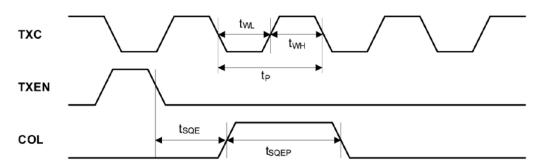

| Figure 9.  | MII SQE Timing (10Base-T)                                            | 44 |

| Figure 10. | MII Transmit Timing (10Base-T)                                       | 45 |

| Figure 11. | MII Receive Timing (10Base-T)                                        | 46 |

| Figure 12. | MII Transmit Timing (100Base-TX)                                     | 47 |

| Figure 13. | MII Receive Timing (100Base-TX)                                      | 48 |

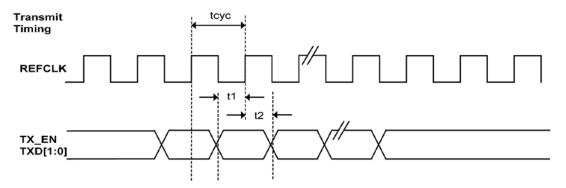

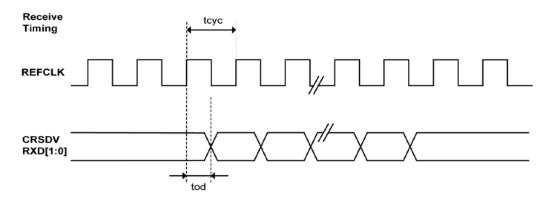

| Figure 14. | RMII Timing – Data Received from RMII                                | 49 |

|            | RMII Timing – Data Input to RMII                                     |    |

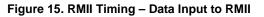

| Figure 16. | Auto-Negotiation Fast Link Pulse (FLP) Timing                        | 50 |

| Figure 17. | MDC/MDIO Timing                                                      | 51 |

|            | Power-Up/Reset Timing                                                |    |

|            | Recommended Reset Circuit                                            |    |

| Figure 20. | Recommended Reset Circuit for interfacing with CPU/FPGA Reset Output | 53 |

| Figure 21. | Reference Circuits for LED Strapping Pins                            | 54 |

# List of Tables

| Table 1.  | MII Management Frame Format                                                      | 23  |

|-----------|----------------------------------------------------------------------------------|-----|

| Table 2.  | MII Signal Definition                                                            | .24 |

| Table 3.  | RMII Signal Description – KSZ8041NL                                              | .26 |

| Table 4.  | RMII Signal Description – KSZ8041RNL                                             | 26  |

| Table 5.  | MDI/MDI-X Pin Description                                                        | 28  |

| Table 6.  | KSZ8041NL/RNL Power Pin Description                                              | 31  |

| Table 7.  | MII SQE Timing (10Base-T) Parameters                                             | 44  |

| Table 8.  | MII Transmit Timing (10Base-T) Parameters                                        | 45  |

| Table 9.  | MII Receive Timing (10Base-T) Parameters                                         | .46 |

| Table 10. | MII Transmit Timing (100Base-TX) Parameters                                      | 47  |

| Table 11. | MII Receive Timing (100Base-TX) Parameters<br>RMII Timing Parameters – KSZ8041NL | 48  |

| Table 12. | RMII Timing Parameters – KSZ8041NL                                               | 49  |

| Table 13. | RMII Timing Parameters – KSZ8041RNL                                              | .49 |

| Table 14. | Auto-Negotiation Fast Link Pulse (FLP) Timing Parameters                         | 50  |

| Table 15. | Auto-Negotiation Fast Link Pulse (FLP) Timing Parameters                         | 51  |

| Table 16. | Power-Up/Reset Timing Parameters                                                 | .52 |

| Table 17. | Transformer Selection Criteria                                                   | 55  |

| Table 18. | Qualified Single Port Magnetics                                                  | 55  |

| Table 19. | Typical Reference Crystal Characteristics                                        | 55  |

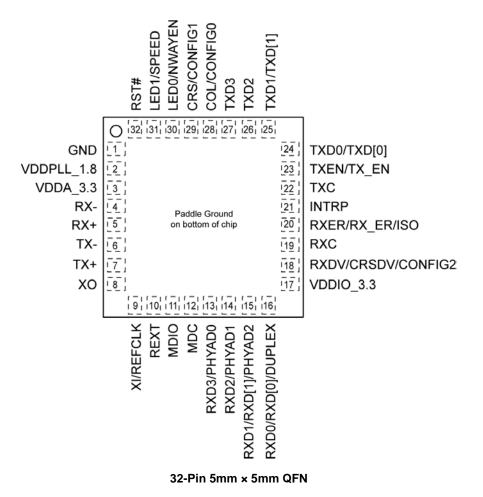

# Pin Configuration – KSZ8041NL

## **Pin Description – KSZ8041NL**

| Pin<br>Number | Pin<br>Name      | Type <sup>(2)</sup> | Pin Function                                                                                                                                                                                             |

|---------------|------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | GND              | Gnd                 | Ground.                                                                                                                                                                                                  |

| 2             | VDDPLL_1.8       | Р                   | 1.8V Analog $V_{DD}$<br>Decouple with 1.0µF and 0.1µF capacitors to ground.                                                                                                                              |

| 3             | VDDA_3.3         | Р                   | 3.3V Analog V <sub>DD</sub> .                                                                                                                                                                            |

| 4             | RX-              | I/O                 | Physical receive or transmit signal (- differential).                                                                                                                                                    |

| 5             | RX+              | I/O                 | Physical receive or transmit signal (+ differential).                                                                                                                                                    |

| 6             | TX-              | I/O                 | Physical transmit or receive signal (- differential).                                                                                                                                                    |

| 7             | TX+              | I/O                 | Physical transmit or receive signal (+ differential).                                                                                                                                                    |

| 8             | хо               | О                   | Crystal Feedback.<br>This pin is used only in MII mode when a 25MHz crystal is used.<br>This pin is a no connect if oscillator or external clock source is used, or if RMII mode is<br>selected.         |

| 9             | XI /<br>REFCLK   | I                   | Crystal / Oscillator / External Clock Input:<br>MII Mode: 25MHz ±50ppm (crystal, oscillator, or external clock)<br>RMII Mode: 50MHz ±50ppm (oscillator, or external clock only)                          |

| 10            | REXT             | I/O                 | Set physical transmit output current.<br>Connect a $6.49K\Omega$ resistor in parallel with a 100pF capacitor to ground on this pin. See KSZ8041NL reference schematics.                                  |

| 11            | MDIO             | I/O                 | Management Interface (MII) Data I/O<br>This pin requires an external 4.7KΩ pull-up resistor.                                                                                                             |

| 12            | MDC              | I                   | Management Interface (MII) Clock Input<br>This pin is synchronous to the MDIO data interface.                                                                                                            |

| 13            | RXD3 /<br>PHYAD0 | lpu/O               | MII Mode: Receive Data Output[3] <sup>(3)</sup> /.<br>Config Mode: The pull-up/pull-down value is latched as PHYADDR[0] during power-up / reset. See <i>Strapping Options – KSZ8041NL</i> for details.   |

| 14            | RXD2 /<br>PHYAD1 | lpd/O               | MII Mode: Receive Data Output[2] <sup>(3)</sup> /<br>Config Mode: The pull-up/pull-down value is latched as PHYADDR[1] during power-up /<br>reset. See <i>Strapping Options – KSZ8041NL</i> for details. |

#### Notes:

2. P = Power supply.

- Gnd = Ground.

- I = Input.

- O = Output.I/O = Bi-directional.

Ipd = Input with internal pull-down (40K +/-30%).

Ipu = Input with internal pull-up (40K +/-30%).

$\dot{O}$ pu =  $\dot{O}$ utput with internal pull-up (40K +/-30%).

Ipu/O = Input with internal pull-up (40K +/-30%) during power-up/reset; output pin otherwise.

Ipd/O = Input with internal pull-down (40K +/-30%) during power-up/reset; output pin otherwise.

- 3. MII Rx Mode: The RXD[3..0] bits are synchronous with RXCLK. When RXDV is asserted, RXD[3..0] presents valid data to MAC through the MII. RXD[3..0] is invalid when RXDV is de-asserted.

- 4. RMII Rx Mode: The RXD[1:0] bits are synchronous with REF\_CLK. For each clock period in which CRS\_DV is asserted, two bits of recovered data are sent from the PHY.

- 5. MII Tx Mode: The TXD[3..0] bits are synchronous with TXCLK. When TXEN is asserted, TXD[3..0] presents valid data from the MAC through the MII. TXD[3..0] has no effect when TXEN is de-asserted.

- 6. RMII Tx Mode: The TXD[1:0] bits are synchronous with REF\_CLK. For each clock period in which TX\_EN is asserted, two bits of data are received by the PHY from the MAC.

# Pin Description – KSZ8041NL (Continued)

| Pin<br>Number | Pin<br>Name                  | Type <sup>(2)</sup> | Pin Function                                                                                                                                                                                                                                                                   |

|---------------|------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15            | RXD1 /<br>RXD[1] /<br>PHYAD2 | lpd/O               | MII Mode: Receive Data Output[1] <sup>(3)</sup> /.<br>RMII Mode: Receive Data Output[1] <sup>(4)</sup> /.<br>Config Mode: The pull-up/pull-down value is latched as PHYADDR[2] during power-up /<br>reset. See <i>Strapping Options – KSZ8041NL</i> for details.               |

| 16            | RXD0 /<br>RXD[0] /<br>DUPLEX | lpu/O               | MII Mode: Receive Data Output[0] <sup>(3)</sup> /.<br>RMII Mode: Receive Data Output[0] <sup>(4)</sup> /.<br>Config Mode: Latched as DUPLEX (register 0h, bit 8) during power-up / reset. See<br><i>Strapping Options – KSZ8041NL</i> for details.                             |

| 17            | VDDIO_3.3                    | Р                   | 3.3V Digital V <sub>DD</sub> .                                                                                                                                                                                                                                                 |

| 18            | RXDV /<br>CRSDV /<br>CONFIG2 | lpd/O               | MII Mode: Receive Data Valid Output /.<br>RMII Mode: Carrier Sense/Receive Data Valid Output /.<br>Config Mode: The pull-up/pull-down value is latched as CONFIG2 during power-up / reset.<br>See Strapping Options – KSZ8041NL for details.                                   |

| 19            | RXC                          | 0                   | MII Mode: Receive Clock Output.                                                                                                                                                                                                                                                |

| 20            | RXER /<br>RX_ER /<br>ISO     | lpd/O               | MII Mode: Receive Error Output.<br>RMII Mode: Receive Error Output.<br>Config Mode: The pull-up/pull-down value is latched as ISOLATE during power-up / reset.<br>See Strapping Options – KSZ8041NL for details.                                                               |

| 21            | INTRP                        | Opu                 | Interrupt Output: Programmable Interrupt Output<br>Register 1Bh is the Interrupt Control/Status Register for programming the interrupt<br>conditions and reading the interrupt status. Register 1Fh bit 9 sets the interrupt output to<br>active low (default) or active high. |

| 22            | TXC                          | 0                   | MII Mode: Transmit Clock Output.                                                                                                                                                                                                                                               |

| 23            | TXEN /<br>TX_EN              | I                   | MII Mode: Transmit Enable Input /.<br>RMII Mode: Transmit Enable Input.                                                                                                                                                                                                        |

| 24            | TXD0 /<br>TXD[0]             | I                   | MII Mode: Transmit Data Input[0] <sup>(5)</sup> /.<br>RMII Mode: Transmit Data Input[0] <sup>(6)</sup> .                                                                                                                                                                       |

| 25            | TXD1 /<br>TXD[1]             | I                   | MII Mode: Transmit Data Input[1] <sup>(5)</sup> /.<br>RMII Mode: Transmit Data Input[1] <sup>(6)</sup> .                                                                                                                                                                       |

| 26            | TXD2                         | I                   | MII Mode: Transmit Data Input[2] <sup>(5)</sup> /.                                                                                                                                                                                                                             |

| 27            | TXD3                         | I                   | MII Mode: Transmit Data Input[3] <sup>(5)</sup> /.                                                                                                                                                                                                                             |

| 28            | COL /<br>CONFIG0             | lpd/O               | MII Mode: Collision Detect Output /.<br>Config Mode: The pull-up/pull-down value is latched as CONFIG0 during power-up / reset.<br>See <i>Strapping Options – KSZ8041NL</i> for details.                                                                                       |

| 29            | CRS /<br>CONFIG1             | lpd/O               | MII Mode: Carrier Sense Output /.<br>Config Mode: The pull-up/pull-down value is latched as CONFIG1 during power-up / reset.<br>See Strapping Options – KSZ8041NL for details.                                                                                                 |

# Pin Description – KSZ8041NL (Continued)

| Pin<br>Number | Pin<br>Name | Type <sup>(2)</sup>                                                                                                                                                                                                                                                                                          | Pin Function                                                             |           |                |  |

|---------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------|----------------|--|

|               |             | LED Output: Programmable LED0 Output /.<br>Config Mode: Latched as Auto-Negotiation Enable (register 0h, bit 12) during power-up / reset. See <i>Strapping Options – KSZ8041NL</i> for details.<br>The LED0 pin is programmable via register 1Eh bits [15:14], and is defined as follows:<br>LED Mode = [00] |                                                                          |           |                |  |

|               |             |                                                                                                                                                                                                                                                                                                              | Link/Activity                                                            | Pin State | LED Definition |  |

|               |             | Ipu/O                                                                                                                                                                                                                                                                                                        | No Link                                                                  | Н         | OFF            |  |

|               |             |                                                                                                                                                                                                                                                                                                              | Link                                                                     | L         | ON             |  |

|               | LED0 /      |                                                                                                                                                                                                                                                                                                              | Activity                                                                 | Toggle    | Blinking       |  |

| 30            | NWAYEN      |                                                                                                                                                                                                                                                                                                              | LED Mode = [01]                                                          |           |                |  |

|               |             |                                                                                                                                                                                                                                                                                                              | Link                                                                     | Pin State | LED Definition |  |

|               |             |                                                                                                                                                                                                                                                                                                              | No Link                                                                  | Н         | OFF            |  |

|               |             |                                                                                                                                                                                                                                                                                                              | Link                                                                     | L         | ON             |  |

|               |             |                                                                                                                                                                                                                                                                                                              | <u>LED Mode = [10]</u><br>Reserved<br><u>LED Mode = [11]</u><br>Reserved |           |                |  |

# Pin Description – KSZ8041NL (Continued)

| Pin<br>Number | Pin<br>Name     | Type <sup>(2)</sup> | Pin Function                                               |                                          |                                                     |                                                       |

|---------------|-----------------|---------------------|------------------------------------------------------------|------------------------------------------|-----------------------------------------------------|-------------------------------------------------------|

|               |                 | Ipu/O               | Config Mode: La Strapping Option                           | ns – KSZ8041NL for<br>programmable via i | egister 0h, bit 13) during<br><sup>-</sup> details. | power-up / reset. See<br>, and is defined as follows: |

| 31            | LED1 /<br>SPEED |                     | LED Mode = [01]                                            |                                          |                                                     | ]                                                     |

|               |                 |                     | Activity                                                   | Pin State                                | LED Definition                                      |                                                       |

|               |                 |                     | No Activity                                                | Н                                        | OFF                                                 |                                                       |

|               |                 |                     | Activity                                                   | Toggle                                   | Blinking                                            |                                                       |

|               |                 |                     | LED Mode = [1]<br>Reserved.<br>LED Mode = [1]<br>Reserved. |                                          |                                                     |                                                       |

| 32            | RST#            | I                   | Chip Reset (acti                                           | ve low).                                 |                                                     |                                                       |

| PADDLE        | GND             | Gnd                 | Ground.                                                    |                                          |                                                     |                                                       |

## **Strapping Options – KSZ8041NL**

Pin strap-ins are latched during power-up or reset. In some systems, the MAC receive input pins may drive high during power-up or reset, and consequently cause the PHY strap-in pins on the MII/RMII signals to be latched high. In this case, it is recommended to add 1K pull-downs on these PHY strap-in pins to ensure the PHY does not strap-in to ISOLATE mode, or is not configured with an incorrect PHY Address.

| Pin<br>Number | Pin<br>Name | Type <sup>(7)</sup> | Pin Function                                                                                 | Pin Function                                                                         |                                                                            |  |  |  |  |

|---------------|-------------|---------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| 15            | PHYAD2      | lpd/O               | The PHY Address is latched at power-up / reset and is configurable to any value from 1 to 7. |                                                                                      |                                                                            |  |  |  |  |

| 14            | PHYAD1      | lpd/O               | The default PHY                                                                              | The default PHY Address is 00001.                                                    |                                                                            |  |  |  |  |

| 13            | PHYAD0      | lpu/O               | PHY Address bits                                                                             | PHY Address bits [4:3] are always set to '00'.                                       |                                                                            |  |  |  |  |

|               |             |                     | The CONFIG[2:0]                                                                              | ] strap-in pins are latched at power-up                                              | / reset and are defined as follows:                                        |  |  |  |  |

|               |             |                     | CONFIG[2:0]                                                                                  | Mode                                                                                 |                                                                            |  |  |  |  |

|               |             |                     | 000                                                                                          | MII (default)                                                                        |                                                                            |  |  |  |  |

| 18            | CONFIG2     | lpd/O               | 001                                                                                          | RMII                                                                                 |                                                                            |  |  |  |  |

| 29            | CONFIG1     | Ipd/O               | 010                                                                                          | Reserved – not used                                                                  |                                                                            |  |  |  |  |

| 28            | CONFIG0     | lpd/O               | 011                                                                                          | Reserved – not used                                                                  |                                                                            |  |  |  |  |

|               |             |                     | 100                                                                                          | MII 100Mbps Preamble Restore                                                         |                                                                            |  |  |  |  |

|               |             |                     | 101                                                                                          | Reserved – not used                                                                  |                                                                            |  |  |  |  |

|               |             |                     | 110                                                                                          | Reserved – not used                                                                  |                                                                            |  |  |  |  |

|               |             |                     | 111                                                                                          | Reserved – not used                                                                  |                                                                            |  |  |  |  |

|               |             | lpd/O               | ISOLATE Mode:                                                                                | ·                                                                                    |                                                                            |  |  |  |  |

| 20            | ISO         |                     | Pull-up =                                                                                    | = Enable                                                                             |                                                                            |  |  |  |  |

| 20            | 150         |                     | Pull-dow                                                                                     | /n (default) = Disable                                                               |                                                                            |  |  |  |  |

|               |             |                     | During power-up                                                                              | / reset, this pin value is latched into re                                           | gister 0h bit 10.                                                          |  |  |  |  |

|               |             |                     | SPEED Mode:                                                                                  |                                                                                      |                                                                            |  |  |  |  |

|               |             |                     |                                                                                              | default) = 100Mbps                                                                   |                                                                            |  |  |  |  |

| 31            | SPEED       | lpu/O               |                                                                                              | n = 10Mbps                                                                           |                                                                            |  |  |  |  |

|               |             |                     |                                                                                              | / reset, this pin value is latched into re<br>o register 4h (Auto-Negotiation Advert | gister 0h bit 13 as the Speed Select, and isement) as the Speed capability |  |  |  |  |

|               |             |                     | DUPLEX Mode:                                                                                 |                                                                                      |                                                                            |  |  |  |  |

| 16            | DUPLEX      | lpu/O               | Pull-up (default) = Half Duplex                                                              |                                                                                      |                                                                            |  |  |  |  |

| 10            | DOILEX      | ipu/O               | Pull-down = Full Duplex                                                                      |                                                                                      |                                                                            |  |  |  |  |

|               |             |                     |                                                                                              | / reset, this pin value is latched into re                                           | gister 0h bit 8 as the Duplex Mode.                                        |  |  |  |  |

|               |             |                     | Nway Auto-Nego                                                                               |                                                                                      |                                                                            |  |  |  |  |

| 30            | NWAYEN      | l Ipu/O             | Pull-up (default) = Enable Auto-Negotiation                                                  |                                                                                      |                                                                            |  |  |  |  |

|               |             |                     |                                                                                              | n = Disable Auto-Negotiation                                                         |                                                                            |  |  |  |  |

|               |             |                     | During power-up                                                                              | / reset, this pin value is latched into re                                           | gister un dit 12.                                                          |  |  |  |  |

Note:

7. Ipu/O = Input with internal pull-up (40K +/-30%) during power-up/reset; output pin otherwise.

Ipd/O = Input with internal pull-down (40K +/-30%) during power-up/reset; output pin otherwise.

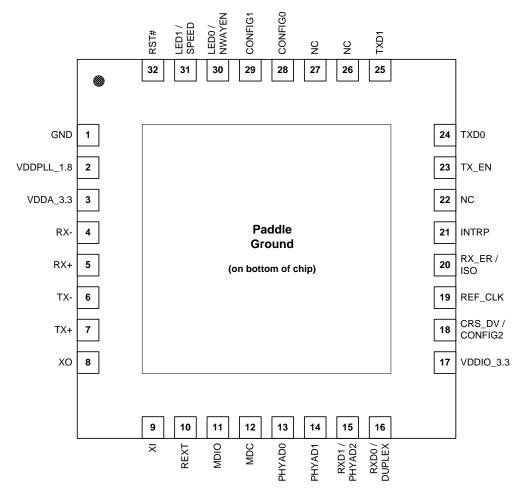

# Pin Configuration – KSZ8041RNL

32-Pin 5mm × 5mm QFN

## **Pin Description – KSZ8041RNL**

| Pin<br>Number | Pin<br>Name      | Type <sup>(8)</sup> | Pin Function                                                                                                                                                                                                    |

|---------------|------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | GND              | Gnd                 | Ground.                                                                                                                                                                                                         |

| 2             | VDDPLL_1.8       | Р                   | 1.8V Analog $V_{DD}$ .<br>Decouple with 1.0µF and 0.1µF capacitors to ground.                                                                                                                                   |

| 3             | VDDA_3.3         | Р                   | 3.3V Analog V <sub>DD</sub> .                                                                                                                                                                                   |

| 4             | RX-              | I/O                 | Physical receive or transmit signal (- differential).                                                                                                                                                           |

| 5             | RX+              | I/O                 | Physical receive or transmit signal (+ differential).                                                                                                                                                           |

| 6             | TX-              | I/O                 | Physical transmit or receive signal (- differential).                                                                                                                                                           |

| 7             | TX+              | I/O                 | Physical transmit or receive signal (+ differential).                                                                                                                                                           |

| 8             | хо               | О                   | Crystal Feedback – for 25MHz Crystal.<br>This pin is a no connect if oscillator or external clock source is used.                                                                                               |

| 9             | XI               | I                   | Crystal / Oscillator / External Clock Input.<br>25MHz ±50ppm.                                                                                                                                                   |

| 10            | REXT             | I/O                 | Set physical transmit output current.<br>Connect a $6.49K\Omega$ resistor in parallel with a 100pF capacitor to ground on this pin. See KSZ8041RNL reference schematics.                                        |

| 11            | MDIO             | I/O                 | Management Interface (MII) Data I/O.<br>This pin requires an external 4.7KΩ pull-up resistor.                                                                                                                   |

| 12            | MDC              | I                   | Management Interface (MII) Clock Input.<br>This pin is synchronous to the MDIO data interface.                                                                                                                  |

| 13            | PHYAD0           | lpu/O               | The pull-up/pull-down value is latched as PHYADDR[0] during power-up / reset. See<br><i>Strapping Options – KSZ8041RNL</i> for details.                                                                         |

| 14            | PHYAD1           | lpd/O               | The pull-up/pull-down value is latched as PHYADDR[1] during power-up / reset. See <i>Strapping Options – KSZ8041RNL</i> for details.                                                                            |

| 15            | RXD1 /<br>PHYAD2 | lpd/O               | RMII Mode: RMII Receive Data Output[1] <sup>(9)</sup> /<br>Config Mode: The pull-up/pull-down value is latched as PHYADDR[2] during power-up /<br>reset. See <i>Strapping Options – KSZ8041RNL</i> for details. |

| 16            | RXD0 /<br>DUPLEX | lpu/O               | RMII Mode: RMII Receive Data Output[0] <sup>(9)</sup> /<br>Config Mode: Latched as DUPLEX (register 0h, bit 8) during power-up / reset. See<br><i>Strapping Options – KSZ8041RNL</i> for details.               |

Notes:

8. P = Power supply.

Gnd = Ground.

I = Input.O = Output.

I/O = Bi-directional.

Opu = Output with internal pull-up (40K  $\pm$ 30%).

Ipu/O = Input with internal pull-up (40K ±30%) during power-up/reset; output pin otherwise.

Ipd/O = Input with internal pull-down (40K ±30%) during power-up/reset; output pin otherwise.

9. RMII Rx Mode: The RXD[1:0] bits are synchronous with REF\_CLK. For each clock period in which CRS\_DV is asserted, two bits of recovered data are sent from the PHY.

# Pin Description – KSZ8041RNL (Continued)

| Pin<br>Number | Pin<br>Name         | Type <sup>(8)</sup> | Pin Function                                                                                                                                                                                                                                                                    |  |

|---------------|---------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 17            | VDDIO_3.3           | Р                   | 3.3V Digital V <sub>DD</sub>                                                                                                                                                                                                                                                    |  |

| 18            | CRS_DV /<br>CONFIG2 | lpd/O               | RMII Mode: Carrier Sense/Receive Data Valid Output /.<br>Config Mode: The pull-up/pull-down value is latched as CONFIG2 during power-up / reset.<br>See <i>Strapping Options – KSZ8041RNL</i> for details.                                                                      |  |

| 19            | REF_CLK             | 0                   | 50MHz Clock Output.<br>This pin provides the 50MHz RMII reference clock output to the MAC.                                                                                                                                                                                      |  |

| 20            | RX_ER /<br>ISO      | lpd/O               | RMII Mode: RMII Receive Error Output /<br>Config Mode: The pull-up/pull-down value is latched as ISOLATE during power-up / reset.<br>See <i>Strapping Options – KSZ8041RNL</i> for details.                                                                                     |  |

| 21            | INTRP               | Opu                 | Interrupt Output: Programmable Interrupt Output.<br>Register 1Bh is the Interrupt Control/Status Register for programming the interrupt<br>conditions and reading the interrupt status. Register 1Fh bit 9 sets the interrupt output to<br>active low (default) or active high. |  |

| 22            | NC                  | 0                   | No Connect.                                                                                                                                                                                                                                                                     |  |

| 23            | TX_EN               | I                   | RMII Transmit Enable Input.                                                                                                                                                                                                                                                     |  |

| 24            | TXD0                | I                   | RMII Transmit Data Input[0] <sup>(10)</sup> .                                                                                                                                                                                                                                   |  |

| 25            | TXD1                | I                   | RMII Transmit Data Input[1] <sup>(10)</sup> .                                                                                                                                                                                                                                   |  |

| 26            | NC                  | I                   | No Connect.                                                                                                                                                                                                                                                                     |  |

| 27            | NC                  | I                   | No Connect.                                                                                                                                                                                                                                                                     |  |

| 28            | CONFIG0             | Ipd/O               | The pull-up/pull-down value is latched as CONFIG0 during power-up / reset. See <i>Strapping Options – KSZ8041RNL</i> for details.                                                                                                                                               |  |

| 29            | CONFIG1             | lpd/O               | The pull-up/pull-down value is latched as CONFIG1 during power-up / reset. See <i>Strapping Options – KSZ8041RNL</i> for details.                                                                                                                                               |  |

#### Note:

10. RMII Tx Mode: The TXD[1:0] bits are synchronous with REF\_CLK. For each clock period in which TX\_EN is asserted, two bits of data are received by the PHY from the MAC.

# Pin Description – KSZ8041RNL (Continued)

| Pin<br>Number | Pin<br>Name     | Type <sup>(8)</sup> | Pin Function                         |                                          |                                                    |                                                                |

|---------------|-----------------|---------------------|--------------------------------------|------------------------------------------|----------------------------------------------------|----------------------------------------------------------------|

|               |                 |                     | Config Mode: Lat<br>reset. See Strap | bing Options – KŠ2<br>programmable via i | otiation Enable (register<br>Z8041RNL for details. | 0h, bit 12) during power-up /<br>l, and is defined as follows: |

|               |                 |                     | LED Mode = [0                        | Pin State                                | LED Definition                                     | -                                                              |

|               |                 |                     | No Link                              | H                                        | OFF                                                |                                                                |

|               |                 |                     | Link                                 |                                          | ON                                                 | -                                                              |

| 30            | LED0 /          | lpu/O               |                                      |                                          |                                                    | -                                                              |

|               | NWAYEN          |                     | Activity                             | Toggle                                   | Blinking                                           |                                                                |

|               |                 |                     | LED Mode = [0                        | 1]                                       |                                                    | ]                                                              |

|               |                 |                     | Link                                 | Pin State                                | LED Definition                                     |                                                                |

|               |                 |                     | No Link                              | Н                                        | OFF                                                |                                                                |

|               |                 |                     | Link                                 | L                                        | ON                                                 |                                                                |

|               |                 |                     | Config Mode: Lat<br>Strapping Option | s – KSZ8041RNL f                         | egister 0h, bit 13) during<br>or details.          | g power-up / reset. See<br> , and is defined as follows:       |

|               |                 |                     | LED Mode = [00]                      |                                          |                                                    |                                                                |

|               |                 |                     | Speed                                | Pin State                                | LED Definition                                     |                                                                |

|               |                 | lpu/O               | 10BT                                 | н                                        | OFF                                                | _                                                              |

| 31            | LED1 /<br>SPEED |                     | 100BT                                | L                                        | ON                                                 |                                                                |

|               |                 |                     | LED Mode = [0                        | 1]                                       |                                                    | ]                                                              |

|               |                 |                     | Activity                             | Pin State                                | LED Definition                                     |                                                                |

|               |                 |                     | No Activity                          | Н                                        | OFF                                                | 1                                                              |

|               |                 |                     | Activity                             | Toggle                                   | Blinking                                           | ]                                                              |

|               |                 |                     | LED Mode = [10]<br>Reserved.         | . [11]                                   |                                                    |                                                                |

| 32            | RST#            | Ι                   | Chip Reset (activ                    | e low).                                  |                                                    |                                                                |

| PADDLE        | GND             | Gnd                 | Ground.                              |                                          |                                                    |                                                                |

## **Strapping Options – KSZ8041RNL**

Pin strap-ins are latched during power-up or reset. In some systems, the MAC receive input pins may drive high during power-up or reset, and consequently cause the PHY strap-in pins on the RMII signals to be latched high. In this case, it is recommended to add 1K pull-downs on these PHY strap-in pins to ensure the PHY does not strap-in to ISOLATE mode, or is not configured with an incorrect PHY Address.

| Pin<br>Number | Pin<br>Name | Type <sup>(1)</sup> | Pin Function                                |                                                                                                                                                                |  |  |

|---------------|-------------|---------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 15            | PHYAD2      | Ipd/O               | The PHY Address                             | The PHY Address is latched at power-up / reset and is configurable to any value from 1 to 7.                                                                   |  |  |

| 14            | PHYAD1      | lpd/O               | The default PHY Address is 00001.           |                                                                                                                                                                |  |  |

| 13            | PHYAD0      | lpu/O               | PHY Address bits                            | PHY Address bits [4:3] are always set to '00'.                                                                                                                 |  |  |

|               |             |                     | The CONFIG[2:0]                             | strap-in pins are latched at power-up / reset and are defined as follows:                                                                                      |  |  |

|               |             |                     | CONFIG[2:0]                                 | Mode                                                                                                                                                           |  |  |

|               |             |                     | 000                                         | Reserved – not used                                                                                                                                            |  |  |

| 18            | CONFIG2     | lpd/O               | 001                                         | RMII                                                                                                                                                           |  |  |

| 29            | CONFIG1     | Ipd/O               | 010                                         | Reserved – not used                                                                                                                                            |  |  |

| 28            | CONFIG0     | lpd/O               | 011                                         | Reserved – not used                                                                                                                                            |  |  |

|               |             |                     | 100                                         | Reserved – not used                                                                                                                                            |  |  |

|               |             |                     | 101                                         | Reserved – not used                                                                                                                                            |  |  |

|               |             |                     | 110                                         | Reserved – not used                                                                                                                                            |  |  |

|               |             |                     | 111                                         | Reserved – not used                                                                                                                                            |  |  |

|               |             |                     | ISOLATE Mode:                               | · · · · · · · · · · · · · · · · · · ·                                                                                                                          |  |  |

| 20            | ISO         | lpd/O               | Pull-up =                                   | = Enable                                                                                                                                                       |  |  |

| 20            | 150         | ipu/O               | Pull-dow                                    | /n (default) = Disable                                                                                                                                         |  |  |

|               |             |                     | During power-up                             | / reset, this pin value is latched into register 0h bit 10.                                                                                                    |  |  |

|               |             |                     | SPEED Mode:                                 |                                                                                                                                                                |  |  |

|               |             |                     |                                             | default) = 100Mbps                                                                                                                                             |  |  |

| 31            | SPEED       | lpu/O               |                                             | n = 10Mbps                                                                                                                                                     |  |  |

|               |             |                     |                                             | / reset, this pin value is latched into register 0h bit 13 as the Speed Select,<br>d into register 4h (Auto-Negotiation Advertisement) as the Speed capability |  |  |

|               |             |                     | DUPLEX Mode:                                |                                                                                                                                                                |  |  |

| 16            | DUPLEX      | lpu/O               |                                             | default) = Half Duplex                                                                                                                                         |  |  |

| 10            |             | 190,0               |                                             | n = Full Duplex                                                                                                                                                |  |  |

|               |             |                     |                                             | / reset, this pin value is latched into register 0h bit 8 as the Duplex Mode.                                                                                  |  |  |

|               |             |                     | Nway Auto-Nego                              |                                                                                                                                                                |  |  |

| 30            | NWAYEN      | lpu/O               | Pull-up (default) = Enable Auto-Negotiation |                                                                                                                                                                |  |  |

|               |             |                     |                                             | n = Disable Auto-Negotiation                                                                                                                                   |  |  |

|               |             |                     | During power-up                             | / reset, this pin value is latched into register 0h bit 12.                                                                                                    |  |  |

Note:

11. Ipu/O = Input with internal pull-up (40K +/-30%) during power-up/reset; output pin otherwise.

lpd/O = Input with internal pull-down (40K +/-30%) during power-up/reset; output pin otherwise.

## **Functional Description**

The KSZ8041NL is a single 3.3V supply Fast Ethernet transceiver. It is fully compliant with the IEEE 802.3u Specification.

On the media side, the KSZ8041NL supports 10Base-T and 100Base-TX with HP auto MDI/MDI-X for reliable detection of and correction for straight-through and crossover cables.