## MIC5891

8-Bit Serial-Input Latched Source Driver

#### **General Description**

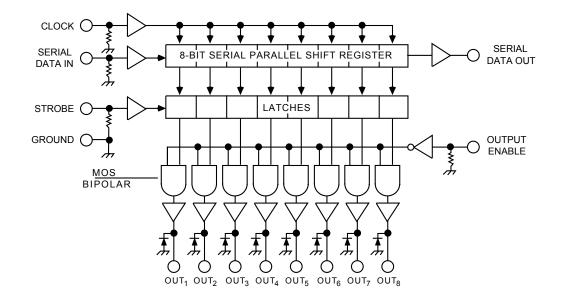

**Functional Diagram**

The MIC5891 latched driver is a high-voltage, high current integrated circuit comprised of eight CMOS data latches, CMOS control circuitry for the common STROBE and OUT-PUT ENABLE, and bipolar Darlington transistor drivers for each latch.

Bipolar/MOS construction provides extremely low power latches with maximum interface flexibility.

The MIC5891 will typically operate at 5MHz with a 5V logic supply.

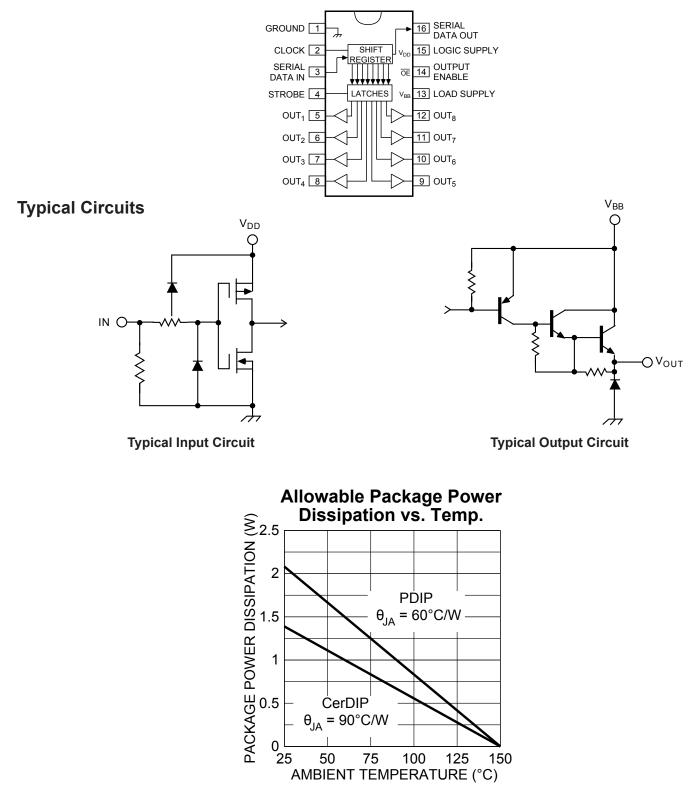

The CMOS inputs are compatible with standard CMOS, PMOS, and NMOS logic levels. TTL circuits may be used with appropriate pull-up resistors to ensure a proper logic-high input.

A CMOS serial data output allows additional drivers to be cascaded when more than 8 bits are required.

The MIC5891 has open-emitter outputs with suppression diodes for protection against inductive load transients. The output transistors are capable of sourcing 500mA and will sustain at least 35V in the on-state.

Simultaneous operation of all drivers at maximum rated current requires a reduction in duty cycle due to package power limitations. Outputs may be paralleled for higher load current capability.

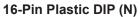

The MIC5891 is available in a 16-pin plastic DIP package (N) and 16-pin wide SOIC package (WM).

#### Features

- · High-voltage, high-current outputs

- Output transient protection diodes

- CMOS-, PMOS-, NMOS-, and TTL-compatible inputs

- 5MHz typical data input rate

- Low-power CMOS latches

#### Applications

- Alphanumeric and bar graph displays

- LED and incandescent displays

- Relay and solenoid drivers

- Other high-power loads

#### **Ordering Information**

| Part | Part Number    |            | Temperature Benge | Package            |  |

|------|----------------|------------|-------------------|--------------------|--|

| Star | andard Pb-Free |            | Temperature Range |                    |  |

| MIC  | 5891BN         | MIC5891YN  | –40°C to +85°C    | 16-Pin Plastic DIP |  |

| MIC  | 5891BWM        | MIC5891YWM | –40°C to +85°C    | 16-Pin Wide SOIC   |  |

### **Pin Configuration**

| Output Voltage (V <sub>OUT</sub> )             | 50V                            |

|------------------------------------------------|--------------------------------|

| Logic Supply Voltage Range (V <sub>DD</sub> )  |                                |

| Load Supply Voltage Range (V <sub>BB</sub> )   |                                |

| Input Voltage Range (V <sub>IN</sub> )         | –0.3V to V <sub>DD</sub> +0.3V |

| Continuous Collector Current (I <sub>c</sub> ) |                                |

| Package Power Dissipation                      |                                |

| Operating Temperature Range (T <sub>A</sub> )  | –55°C to +125°C                |

| Storage Temperature Range (T <sub>s</sub> )    | –65°C to +150°C                |

Note 1:  $T_A = 25^{\circ}C$

**Note 2:** Derate at the rate of 20mW/°C above  $T_A = 25$ °C.

**Note 3:** Micrel CMOS devices have input-static protection but are susceptible to damage when exposed to extremely high static electrical charges.

#### **Allowable Duty Cycles**

| Number of<br>Outputs ON at | Max. Allowable Duty Cycles<br>at T <sub>A</sub> of: |      |      |  |  |

|----------------------------|-----------------------------------------------------|------|------|--|--|

| Ι <sub>ουτ</sub> = -200 mA | 50°C                                                | 60°C | 70°C |  |  |

| 8                          | 53%                                                 | 47%  | 41%  |  |  |

| 7                          | 60%                                                 | 54%  | 48%  |  |  |

| 6                          | 70%                                                 | 64%  | 56%  |  |  |

| 5                          | 83%                                                 | 75%  | 67%  |  |  |

| 4                          | 100%                                                | 94%  | 84%  |  |  |

| 3                          | 100%                                                | 100% | 100% |  |  |

| 2                          | 100%                                                | 100% | 100% |  |  |

| 1                          | 100%                                                | 100% | 100% |  |  |

#### **Electrical Characteristics**

$V_{BB}$  = 50V,  $V_{DD}$  = 5V to 12V;  $T_A$  = +25°C; unless noted.

|                               |                      |                 |                                                     | Limits               |                      |       |

|-------------------------------|----------------------|-----------------|-----------------------------------------------------|----------------------|----------------------|-------|

| Characteristic                | Symbol               | V <sub>BB</sub> | Test Conditions                                     | Min.                 | Max.                 | Units |

| Output Leakage Current        | I <sub>CEX</sub>     | 50V             | T <sub>A</sub> = +25°C                              |                      | -50                  | μA    |

|                               |                      |                 | T <sub>A</sub> = +85°C                              |                      | -100                 | μA    |

| Output Saturation Voltage     | V <sub>CE(SAT)</sub> | 50V             | Ι <sub>ουτ</sub> = –100mA, Τ <sub>A</sub> = +85°C   |                      | 1.8                  | V     |

|                               |                      |                 | Ι <sub>ουτ</sub> = –225mA, Τ <sub>A</sub> = +85°C   |                      | 1.9                  | V     |

|                               |                      |                 | I <sub>out</sub> = –350mA, T <sub>A</sub> = +85°C   |                      | 2.0                  | V     |

| Output Sustaining Voltage     | V <sub>CE(SUS)</sub> | 50V             | Ι <sub>ουτ</sub> = –350mA, L = 2mH                  | 35                   |                      | V     |

| Input Voltage                 | V <sub>IN(1)</sub>   | 50V             | $V_{DD} = 5.0V$                                     | 3.5                  | V <sub>DD</sub> +0.3 | V     |

|                               |                      |                 | $V_{DD} = 12V$                                      | 10.5                 | V <sub>DD</sub> +0.3 | V     |

|                               | V <sub>IN(0)</sub>   | 50V             | $V_{DD} = 5V$ to 12V                                | V <sub>ss</sub> –0.3 | 0.8                  | V     |

| Input Current                 | I <sub>IN(1)</sub>   | 50V             | $V_{DD} = V_{IN} = 5.0V$                            |                      | 50                   | μA    |

|                               |                      |                 | $V_{DD} = 12V$                                      |                      | 240                  | μA    |

| Input Impedance               | Z <sub>IN</sub>      | 50V             | $V_{DD} = 5.0V$                                     | 100                  |                      | kΩ    |

|                               |                      |                 | $V_{DD} = 12V$                                      | 50                   |                      | kΩ    |

| Maximum Clock Frequency       | f <sub>c</sub>       | 50V             |                                                     | 3.3                  |                      | MHz   |

| Serial Data Output Resistance | R <sub>OUT</sub>     | 50V             | $V_{DD} = 5.0V$                                     |                      | 20                   | kΩ    |

|                               |                      |                 | $V_{DD} = 12V$                                      |                      | 6.0                  | kΩ    |

| Turn-On Delay                 | t <sub>PLH</sub>     | 50V             | Output Enable to Output, $I_{OUT} = -350 \text{mA}$ |                      | 2.0                  | μs    |

| Turnoff Delay                 | t <sub>PHL</sub>     | 50V             | Output Enable to Output, $I_{OUT} = -350 \text{mA}$ |                      | 10                   | μs    |

| Supply Current                | I <sub>BB</sub>      | 50V             | all outputs on, all outputs open                    |                      | 10                   | mA    |

|                               |                      |                 | all outputs off                                     |                      | 200                  | μA    |

|                               | I <sub>DD</sub>      | 50V             | $V_{DD}$ = 5V, all outputs off, inputs = 0V         |                      | 100                  | μA    |

|                               |                      |                 | $V_{DD}$ = 12V, all outputs off, inputs = 0V        |                      | 200                  | μA    |

|                               |                      |                 | $V_{DD}$ = 5V, one output on, all inputs = 0V       |                      | 1.0                  | mA    |

|                               |                      |                 | $V_{DD}$ = 12V, one output on, all inputs = 0V      |                      | 3.0                  | mA    |

| Diode Leakage Current         | I <sub>H</sub>       | Max             | T <sub>A</sub> = +25°C                              |                      | 50                   | μA    |

|                               |                      |                 | T <sub>A</sub> = +85°C                              |                      | 100                  | μA    |

| Diode Forward Voltage         | V <sub>F</sub>       | Open            | I <sub>F</sub> = 350mA                              |                      | 2.0                  | V     |

Note 4: Positive (negative) current is defined as going into (coming out of) the specified device pin.

Note 5: Operation of these devices with standard TTL may require the use of appropriate pull-up resistors.

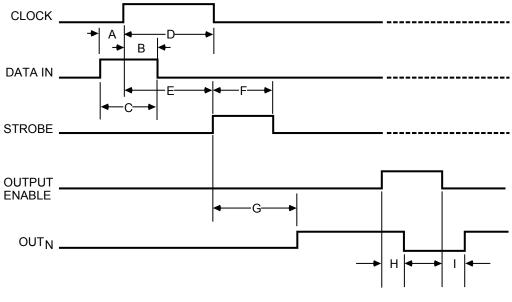

## **Timing Conditions**

|    | $(V_{DD} = 5.0V, Logic Levels are V_{DD} and Ground)$          |                                |

|----|----------------------------------------------------------------|--------------------------------|

| Α. | Minimum data active time before clock pulse (data set-up time) | 75ns                           |

| Β. | Minimum data active time after clock pulse (data hold time)    | 75ns                           |

| C. | Minimum data pulse width                                       | 150ns                          |

| D. | Minimum clock pulse width                                      | 150ns                          |

|    | Minimum time between clock activation and strobe               |                                |

| F. | Minimum strobe pulse width                                     |                                |

| G. | Typical time between strobe activation and output transition   | 1.0µs                          |

|    | Turnoff delay                                                  |                                |

| I. | Turn-on delay                                                  | see Electrical Characteristics |

**Timing Conditions**

## Truth Table

| Serial        |                | Shift Register Contents                |                  | Serial          | Latch Contents                       |                  | Output Content                  |  |  |

|---------------|----------------|----------------------------------------|------------------|-----------------|--------------------------------------|------------------|---------------------------------|--|--|

| Data<br>Input | Clock<br>Input | $I_1 I_2 I_3 \dots I_{N-1} I_N$        | Data<br>Output   | Strobe<br>Input | $I_1 I_2 I_3 \dots I_{N-1} I_n$      | Output<br>Enable | $I_1 I_2 I_3 \dots I_{N-1} I_n$ |  |  |

| Н             |                | $H  R_1  R_2  \dots  R_{N-2}  R_{N-1}$ | R <sub>N-1</sub> |                 |                                      |                  |                                 |  |  |

| L             |                | $L R_1 R_2 R_{N-2} R_{N-1}$            | R <sub>N-1</sub> |                 |                                      |                  |                                 |  |  |

| Х             |                | $R_1 R_2 R_3 \dots R_{N-1} R_N$        | R <sub>N</sub>   |                 |                                      |                  |                                 |  |  |

|               |                | X X X X X                              | Х                | L               | $R_1  R_2  R_3  \dots  R_{N-1}  R_N$ |                  |                                 |  |  |

|               |                | $P_1 P_2 P_3 \dots P_{N-1} P_N$        | P <sub>N</sub>   | Н               | $P_1 P_2 P_3 \dots P_{N-1} P_N$      | L                | $P_1 P_2 P_3 \dots P_{N-1} P_N$ |  |  |

|               |                |                                        |                  |                 | X X X X X                            | Н                | L L L L L                       |  |  |

L = Low Logic Level

H = High Logic Level

X = Irrelevant

P = Present State R = Previous State

**Applications Information**

Serial data present at the input is transferred into the shift register on the rising edge of the CLOCK input pulse. Additional CLOCK pulses shift data information towards the SERIAL DATA OUTPUT. The serial data must appear at the input prior to the rising edge of the CLOCK input waveform.

The 8 bits present in the shift register are transferred to the respective latches when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as

long as the STROBE is held high. Most applications where the latching feature is not used (STROBE tied high) require the OUTPUT ENABLE input to be high during serial data entry.

Outputs are active (controlled by the latch state) when the OUTPUT ENABLE is low. All Outputs are low (disabled) when the OUTPUT ENABLE is high. OUTPUT ENABLE does not affect the data in the shift register or latch.

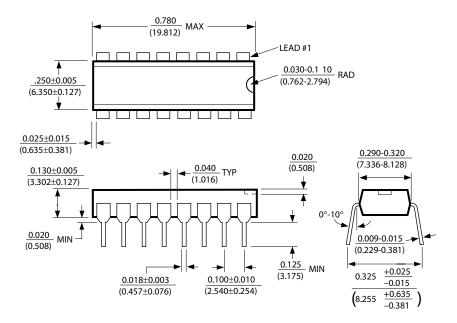

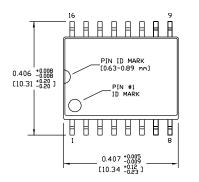

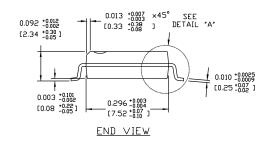

#### **Package Information**

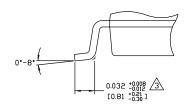

DETAIL "A"

NOTES: 1. DIMENSIONS ARE IN INCHESIMMI. 2. CONTROLLING DIMENSION: INCHES. 3. DIMENSION DOES NOT INCLUDE MOLD FLASH OR PROTRUSIONS, EITHER OF WHICH SHALL NOT EXCEED 0.006[0.15] PER SIDE. 10 Dim Wide St

16-Pin Wide SOIC (WM)

#### MICREL INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA TEL + 1 (408) 944-0800 FAX + 1 (408) 474-1000 WEB http://www.micrel.com

This information furnished by Micrel in this data sheet is believed to be accurate and reliable. However no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 1997 Micrel, Inc.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Micrel:

MIC5891YWM TR MIC5891YWM MIC5891YN