## TMDS341A

SLLS702B-MAY 2006-REVISED MARCH 2007

## 3-TO-1 DVI/HDMI SWITCH

## FEATURES

- Compatible with HDMI 1.3a

- Supports 2.25 Gbps Signaling Rate for 480i/p, 720i/p, and 1080i/p Resolutions up to 12-Bit Color Depth

- Each Port Supports HDMI or DVI Inputs

- Isolated Digital Display Control (DDC) Bus for Unused Ports

- 5-V Tolerance to all DDC and HPD\_SINK Inputs

- Integrated Receiver Termination

- Inter-Pair Output Skew < 100 ps

- Intra-Pair Skew < 50 ps

- 8-dB Receiver Equalization to Compensate for 5-m DVI Cable Losses

- High Impedance Outputs When Disabled

- TMDS Inputs HBM ESD Protection

## DESCRIPTION

Exceeds 5 kV

- 3.3-V Supply Operation

- 80-Pin TQFP Package

- ROHS Compatible and 260°C Reflow Rated

## **APPLICATIONS**

- Switching From Three Digital-Video (DVI) or Digital-Audio Visual (HDMI) Sources

- Digital TV

- Digital Projector

- Audio Video Receiver

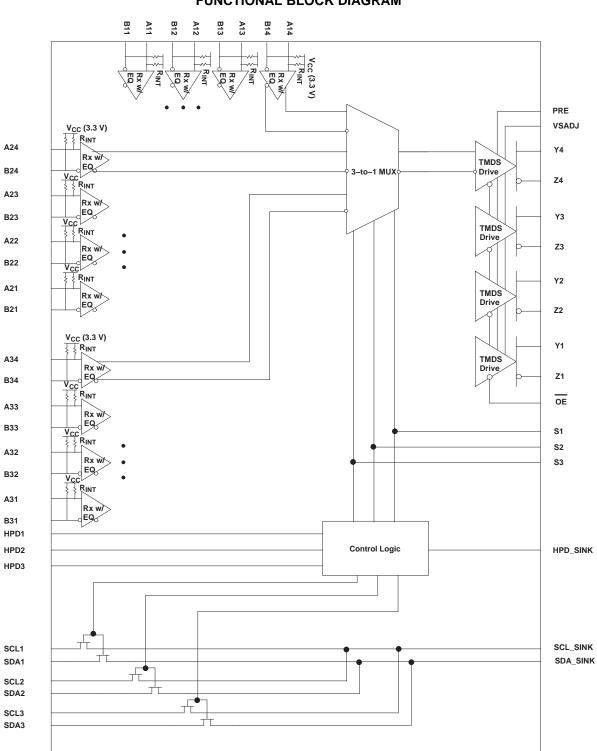

The TMDS341A is a 3-port digital video interface (DVI) or high-definition multimedia interface (HDMI) switch that allows up to 3 DVI or HDMI ports to be switched to a single display terminal. Four TMDS channels, one hot plug detector, and an I<sup>2</sup>C interface are supported on each port. Each TMDS channel allows signaling rates up to 2.25 Gbps.

The active source is selected by configuring source selectors, S1, S2, and S3. The selected TMDS inputs from each port are switched through a 3-to-1 multiplexer. The  $l^2C$  interface of the selected input port is linked to the  $l^2C$  interface of the output port, and the hot plug detector (HPD) of the selected input port is output to HPD\_SINK. For the unused ports, the  $l^2C$  interfaces are isolated, and the HPD pins are kept low.

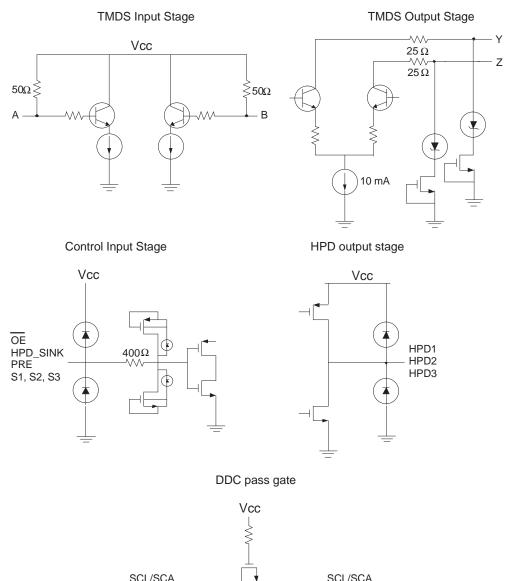

Termination resistors (50- $\Omega$ ), pulled up to V<sub>CC</sub>, are integrated at each receiver input pin. External terminations are not required. A precision resistor is connected externally from the VSADJ pin to ground for setting the differential output voltage to be compliant with the TMDS standard. When the output is connected to a standard TMDS termination and  $\overline{OE}$  is high, the output is high impedance.

The TMDS341A provides fixed 8-dB input equalization and selectable 3-dB output de-emphasis to optimize system performance through 5-meter or longer DVI compliant cables. The device is characterized for operation from 0°C to 70°C.

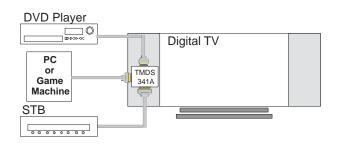

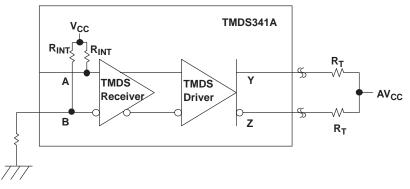

**Typical Application**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## FUNCTIONAL BLOCK DIAGRAM

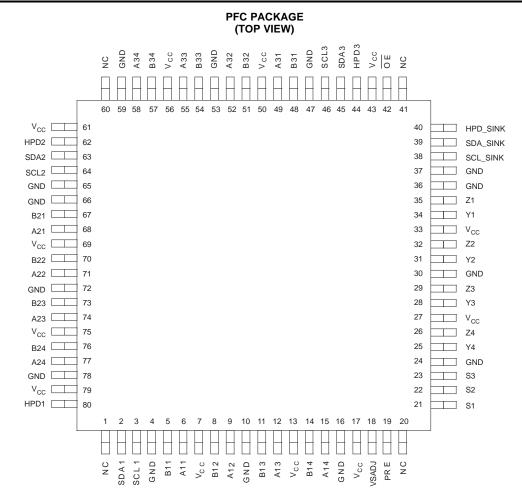

#### **TERMINAL FUNCTIONS**

| TERMINAL           |                                                            |     | DECODIDION                                                                                                                                                                                |

|--------------------|------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | NO.                                                        | I/O | DESCRIPTION                                                                                                                                                                               |

| A11, A12, A13, A14 | 6, 9, 12, 15                                               | I   | Port 1 TMDS positive inputs                                                                                                                                                               |

| A21, A22, A23, A24 | 68, 71, 74, 77                                             | I   | Port 2 TMDS positive inputs                                                                                                                                                               |

| A31, A32, A33, A34 | 49, 52, 55, 58                                             | I   | Port 3 TMDS positive inputs                                                                                                                                                               |

| B11, B12, B13, B14 | 5, 8, 11, 14                                               | I   | Port 1 TMDS negative inputs                                                                                                                                                               |

| B21, B22, B23, B24 | 67, 70, 73, 76                                             | I   | Port 2 TMDS negative inputs                                                                                                                                                               |

| B31, B32, B33, B34 | 48, 51, 54, 57                                             | I   | Port 3 TMDS negative inputs                                                                                                                                                               |

| GND                | 4, 10, 16 24, 30,<br>36, 37, 47, 53,<br>59, 65, 66, 72, 78 |     | Ground                                                                                                                                                                                    |

| HPD1               | 80                                                         | 0   | Port 1 hot plug detector output                                                                                                                                                           |

| HPD2               | 62                                                         | 0   | Port 2 hot plug detector output                                                                                                                                                           |

| HPD3               | 44                                                         | 0   | Port 3 hot plug detector output                                                                                                                                                           |

| HPD_SINK           | 40                                                         | I   | Sink side hot plug detector input<br>High: 5-V power signal asserted from source to sink and EDID is ready<br>Low: No 5-V power signal asserted from source to sink, or EDID is not ready |

| NC                 | 1, 20, 41,60                                               |     | No connect                                                                                                                                                                                |

| ŌE                 | 42                                                         | I   | Output enable, active low                                                                                                                                                                 |

| PRE                | 19                                                         | I   | Output de-emphasis adjustment<br>High: 3 dB<br>Low: 0 dB                                                                                                                                  |

| SCL1               | 3                                                          | I/O | Port 1 DDC bus clock line                                                                                                                                                                 |

| SCL2               | 64                                                         | I/O | Port 2 DDC bus clock line                                                                                                                                                                 |

| SCL3               | 46                                                         | I/O | Port 3 DDC bus clock line                                                                                                                                                                 |

| SCL_SINK           | 38                                                         | I/O | Sink side DDC bus clock line                                                                                                                                                              |

| SDA1               | 2                                                          | I/O | Port 1 DDC bus data line                                                                                                                                                                  |

| SDA2               | 63                                                         | I/O | Port 2 DDC bus data line                                                                                                                                                                  |

| SDA3               | 45                                                         | I/O | Port 3 DDC bus data line                                                                                                                                                                  |

| SDA_SINK           | 39                                                         | I/O | Sink side DDC bus data line                                                                                                                                                               |

| S1, S2, S3         | 21, 22, 23                                                 | Ι   | Source selector input                                                                                                                                                                     |

| V <sub>cc</sub>    | 7, 13, 17 27, 33,<br>43, 50, 56 61, 69,<br>75, 79          |     | Power supply                                                                                                                                                                              |

| VSADJ              | 18                                                         | I   | TMDS compliant voltage swing control                                                                                                                                                      |

| Y1, Y2, Y3, Y4     | 34, 31, 28, 25                                             | 0   | TMDS positive outputs                                                                                                                                                                     |

| Z1, Z2, Z3, Z4     | 35, 32, 29, 26                                             | 0   | TMDS negative outputs                                                                                                                                                                     |

| CONTROL PINS |    |    | I/O SELECTED |                      | HOT PLUG DETECT STATUS |          |          |

|--------------|----|----|--------------|----------------------|------------------------|----------|----------|

| S1           | S2 | S3 | Y/Z          | SCL_SINK<br>SDA_SINK | HPD1                   | HPD2     | HPD3     |

| Н            | x  | x  | A1/B1        | SCL1<br>SDA1         | HPD_SINK               | L        | L        |

| L            | Н  | x  | A2/B2        | SCL2<br>SDA2         | L                      | HPD_SINK | L        |

| L            | L  | н  | A3/B3        | SCL3<br>SDA3         | L                      | L        | HPD_SINK |

| L            | L  | L  | None (Z)     | None (Z)             | L                      | L        | L        |

(1) H: Logic high; L: Logic low; X: Don't care; Z: High impedance

## EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS

SCL/SCA Source

## **ORDERING INFORMATION**<sup>(1)</sup>

| PART NUMBER  | PART MARKING | PACKAGE               |

|--------------|--------------|-----------------------|

| TMDS341APFC  | TMDS341A     | 80-PIN TQFP           |

| TMDS341APFCR | TMDS341A     | 80-PIN TQFP Tape/Reel |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                              |                                                |               | UNIT                            |

|------------------------------|------------------------------------------------|---------------|---------------------------------|

| Supply voltage rai           | nge, V <sub>CC</sub> <sup>(2)</sup>            |               | –0.5 V to 4 V                   |

| Anm <sup>(3)</sup> , Bnm     |                                                |               | 2.5 V to 4 V                    |

| Voltage range                | Ym, Zm, VSADJ, PRE, Sn, OE, HPDn               | -0.5V to 4 V  |                                 |

|                              | SCLn, SCL_SINK, SDAn, SDA_SINK,                | –0.5 V to 6 V |                                 |

|                              | Human body model <sup>(4)</sup>                | Anm, Bnm      | 5 kV                            |

| Electrostatic                |                                                | All pins      | 4 kV                            |

| discharge                    | Charged-device model <sup>(5)</sup> (all pins) | 1000 V        |                                 |

|                              | Machine model <sup>(6)</sup> (all pins)        | 250 V         |                                 |

| Continuous power dissipation |                                                |               | See Dissipation Rating<br>Table |

Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

(3) n = 1, 2, 3; m = 1, 2, 3, 4

(4) Tested in accordance with JEDEC Standard 22, Test Method A114-B

(5) Tested in accordance with JEDEC Standard 22, Test Method C101-A

(6) Tested in accordance with JEDEC Standard 22, Test Method A115-A

#### **DISSIPATION RATINGS**

| PACKAGE | $T_A \le 25^{\circ}C$ | DERATING FACTOR <sup>(1)</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING |

|---------|-----------------------|---------------------------------------------------------------|---------------------------------------|

| 80-TQFP | 1342 mW               | 13.42 mW/°C                                                   | 738 mW                                |

(1) This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

## **RECOMMENDED OPERATING CONDITIONS**

|                     |                                                  | MIN                  | NOM  | MAX                   | UNIT  |

|---------------------|--------------------------------------------------|----------------------|------|-----------------------|-------|

| V <sub>CC</sub>     | Supply voltage                                   | 3                    | 3.3  | 3.6                   | V     |

| T <sub>A</sub>      | Operating free-air temperature                   | 0                    |      | 70                    | °C    |

| TMDS DI             | FFERENTIAL PINS (A/B)                            |                      |      |                       |       |

| V <sub>ID</sub>     | Receiver peak-to-peak differential input voltage | 150                  |      | 1560                  | mVp-p |

| V <sub>IC</sub>     | Input common mode voltage                        | V <sub>CC</sub> -0.4 |      | V <sub>CC</sub> +0.01 | V     |

| R <sub>VSADJ</sub>  | Resistor for TMDS compliant voltage swing range  | 4.6                  | 4.64 | 4.68                  | kΩ    |

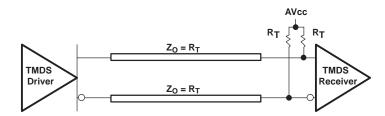

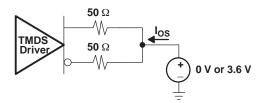

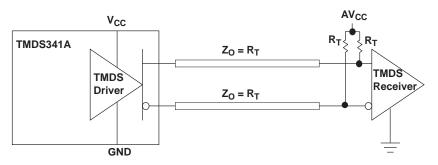

| AV <sub>CC</sub>    | TMDS output termination voltage, see Figure 1    | 3                    | 3.3  | 3.6                   | V     |

| R <sub>T</sub>      | Termination resistance, see Figure 1             | 45                   | 50   | 55                    | Ω     |

|                     | Signaling rate                                   | 0                    |      | 2.25                  | Gbps  |

| CONTRO              | L PINS (PRE; S, OE)                              |                      |      |                       |       |

| V <sub>IH</sub>     | LVTTL High-level input voltage                   | 2                    |      | V <sub>CC</sub>       | V     |

| V <sub>IL</sub>     | LVTTL Low-level input voltage                    | GND                  |      | 0.8                   | V     |

| DDC I/O I           | PINS (SCL, SCL_SINK, SDA, SDA_SINK)              |                      |      |                       |       |

| V <sub>I(DDC)</sub> | Input voltage                                    | GND                  |      | 5.5                   | V     |

|                     | PINS (HPD_SINK)                                  |                      |      |                       |       |

| V <sub>IH</sub>     | LVTTL High-level input voltage                   | 2                    |      | 5.3                   | V     |

| V <sub>IL</sub>     | LVTTL Low-level input voltage                    | GND                  |      | 0.8                   | V     |

## **ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                                                 | TEST CONDITIONS                                                                                                                                                                                                                                       | MIN                   | <b>TYP</b> <sup>(1)</sup> | MAX                   | UNIT                  |

|----------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------|-----------------------|-----------------------|

| I <sub>CC</sub>      | Supply current                                                            | $ \begin{array}{l} V_{IH} = V_{CC}, \ V_{IL} = V_{CC} - 0.4 \ V, \ R_{VSADJ} = 4.64 \ k\Omega, \\ R_T = 50 \ \Omega, \ AV_{CC} = 3.3 \ V \\ Am/Bm = 1.65 \ Gbps \ HDMI \ data \ pattern, \ m = 2, \ 3, \ 4 \\ A1/B1 = 165 \ MHz \ clock \end{array} $ |                       | 190                       | 230                   | mA                    |

| P <sub>D</sub>       | Power dissipation                                                         | $ \begin{array}{l} V_{IH} = V_{CC}, \ V_{IL} = V_{CC} - 0.4 \ V, \ R_{VSADJ} = 4.64 \ k\Omega, \\ R_T = 50 \ \Omega, \ AV_{CC} = 3.3 \ V \\ Am/Bm = 1.65 \ Gbps \ HDMI \ data \ pattern, \ m = 2, \ 3, \ 4 \\ A1/B1 = 165 \ MHz \ clock \end{array} $ |                       | 394                       | 657                   | mW                    |

| TMDS DI              | FFERENTIAL PINS (A/B; Y/Z)                                                |                                                                                                                                                                                                                                                       | 1                     |                           |                       |                       |

| V <sub>OH</sub>      | Single-ended high-level output voltage                                    |                                                                                                                                                                                                                                                       | AV <sub>CC</sub> -10  |                           | AV <sub>CC</sub> +10  | mV                    |

| V <sub>OL</sub>      | Single-ended low-level output voltage                                     | -                                                                                                                                                                                                                                                     | AV <sub>CC</sub> -600 |                           | AV <sub>CC</sub> -400 | mV                    |

| V <sub>swing</sub>   | Single-ended output swing voltage                                         |                                                                                                                                                                                                                                                       | 400                   |                           | 600                   | mV                    |

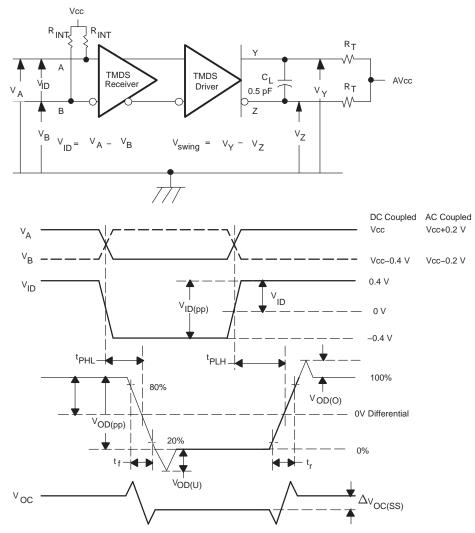

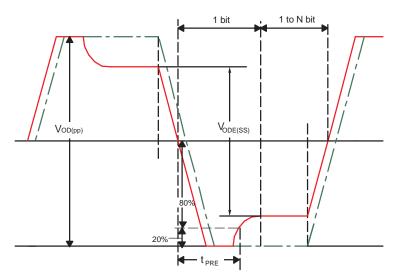

| V <sub>OD(O)</sub>   | Overshoot of output differential voltage                                  | See Figure 2, $AV_{CC} = 3.3 V$ ,<br>$R_T = 50 \Omega$ , PRE = 0 V                                                                                                                                                                                    |                       | 6%                        | 15%                   | 2× V <sub>swing</sub> |

| V <sub>OD(U)</sub>   | Undershoot of output differential voltage                                 |                                                                                                                                                                                                                                                       |                       | 12%                       | 25%                   | 2× V <sub>swing</sub> |

| $\Delta V_{OC(SS)}$  | Change in steady-state common-mode<br>output voltage between logic states |                                                                                                                                                                                                                                                       |                       | 0.5                       | 5                     | mV                    |

| I <sub>(O)OFF</sub>  | Single-ended standby output current                                       | $\begin{array}{l} 0 \ V \leq V_{CC} \leq 1.5 \ V, \\ AV_{CC} = 3.3 \ V, \ R_T = 50 \ \Omega \end{array} \end{array} \label{eq:VCC}$                                                                                                                   | -10                   |                           | 10                    | μA                    |

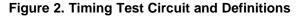

| I <sub>(OS)</sub>    | Short circuit output current                                              | See Figure 3                                                                                                                                                                                                                                          |                       |                           | 12                    | mA                    |

| V <sub>ODE(SS)</sub> | Steady state output differential voltage with de-emphasis                 | See Figure 4, PRE = $V_{CC}$ ,<br>Am/Bm = 250 Mbps HDMI data pattern, m = 2, 3, 4                                                                                                                                                                     | 560                   |                           | 840                   | mVp-p                 |

| V <sub>ODE(pp)</sub> | Peak-to-peak output differential voltage                                  | A1/B1 = 25 MHz clock                                                                                                                                                                                                                                  | 800                   |                           | 1200                  | mVp-p                 |

| V <sub>I(open)</sub> | Single-ended input voltage under high<br>impedance input or open input    | I <sub>I</sub> = 10 μA                                                                                                                                                                                                                                | V <sub>CC</sub> -10   |                           | V <sub>CC</sub> +10   | mV                    |

| R <sub>INT</sub>     | Input termination resistance                                              | V <sub>IN</sub> = 2.9 V                                                                                                                                                                                                                               | 45                    | 50                        | 55                    | Ω                     |

| DDC I/O              | PINS (SCL, SCL_SINK, SDA, SDA_SINK)                                       | ·                                                                                                                                                                                                                                                     |                       |                           |                       |                       |

| I <sub>lkg</sub>     | Input leakage current                                                     | $V_I = 0.1 V_{CC}$ to 0.9 $V_{CC}$ to isolated DDC ports                                                                                                                                                                                              |                       | 0.1                       | 2                     | μA                    |

| CIO                  | Input/output capacitance                                                  | $V_1 = 0 V$                                                                                                                                                                                                                                           |                       | 7.5                       |                       | pF                    |

| R <sub>ON</sub>      | Switch resistance                                                         | $I_0 = 3 \text{ mA}, V_0 = 0.4 \text{ V}$                                                                                                                                                                                                             |                       | 25                        | 50                    | Ω                     |

| VPASS                | Switch output voltage                                                     | $V_{I} = 3.3 \text{ V}, I_{O} = 100 \mu\text{A}$                                                                                                                                                                                                      | 1.5 <sup>(2)</sup>    | 2.0                       | 2.5(3)                | V                     |

| STATUS               | PINS (HPD)                                                                |                                                                                                                                                                                                                                                       |                       |                           |                       |                       |

| V <sub>OH(TTL)</sub> | TTL High-level output voltage                                             | $I_{OH} = -8 \text{ mA}$                                                                                                                                                                                                                              | 2.4                   |                           |                       | V                     |

| V <sub>OL(TTL)</sub> | TTL Low-level output voltage                                              | I <sub>OL</sub> = 8 mA                                                                                                                                                                                                                                |                       |                           | 0.4                   | V                     |

| CONTRO               | L PINS (PRE, S, OE)                                                       |                                                                                                                                                                                                                                                       |                       |                           |                       |                       |

| I <sub>IH</sub>      | High-level digital input current                                          | V <sub>IH</sub> = 2 V or V <sub>CC</sub>                                                                                                                                                                                                              |                       | 0.1                       | 2                     | μA                    |

| I <sub>IL</sub>      | Low-level digital input current                                           | V <sub>IL</sub> = GND or 0.8 V                                                                                                                                                                                                                        |                       | 0.1                       | 2                     | μA                    |

| STATUS               | PINS (HPD_SINK)                                                           |                                                                                                                                                                                                                                                       |                       |                           |                       |                       |

|                      | Llick lovel digital input current                                         | V <sub>IH</sub> = 5.3 V                                                                                                                                                                                                                               |                       | 23                        | 100                   |                       |

| I <sub>IH</sub>      | High-level digital input current                                          | V <sub>IH</sub> = 2 V or V <sub>CC</sub>                                                                                                                                                                                                              |                       | 0.1                       | 2                     | μA                    |

| I <sub>IL</sub>      | Low-level digital input current                                           | V <sub>IL</sub> = GND or 0.8 V                                                                                                                                                                                                                        |                       | 0.1                       | 2                     | μA                    |

All typical values are at 25°C and with a 3.3-V supply.

The value is tested in full temperature range at 3.0 V.

The value is tested in full temperature range at 3.6 V.

### SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                                                      | TEST CONDITIONS                                                                                            | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|----------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|------|

| TMDS D               | IFFERENTIAL PINS (Y/Z)                                                         |                                                                                                            |     |                    |     |      |

| t <sub>PLH</sub>     | Propagation delay time, low-to-high-level output                               |                                                                                                            | 250 |                    | 800 | ps   |

| t <sub>PHL</sub>     | Propagation delay time, high-to-low-level output                               |                                                                                                            | 250 |                    | 800 | ps   |

| t <sub>r</sub>       | Differential output signal rise time (20% - 80%)                               |                                                                                                            | 75  |                    | 240 | ps   |

| t <sub>f</sub>       | Differential output signal fall time (20% - 80%)                               | See Figure 2, AV <sub>CC</sub> = 3.3 V,                                                                    | 75  |                    | 240 | ps   |

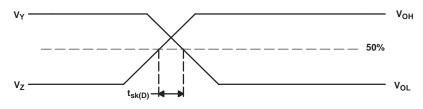

| t <sub>sk(p)</sub>   | Pulse skew ( t <sub>PHL</sub> - t <sub>PLH</sub>  )                            | $R_{T} = 50 \Omega, PRE = 0 V$                                                                             |     | 7                  | 50  | ps   |

| t <sub>sk(D)</sub>   | Intra-pair differential skew, see Figure 5                                     |                                                                                                            |     | 23                 | 50  | ps   |

| t <sub>sk(o)</sub>   | Inter-pair channel-to-channel output skew <sup>(2)</sup>                       |                                                                                                            |     |                    | 100 | ps   |

| t <sub>sk(pp)</sub>  | Part-to-part skew (3)                                                          |                                                                                                            |     |                    | 200 | ps   |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter from Y/Z(1) residual jitter                         | See Figure 8, PRE = 0 V                                                                                    |     | 15                 | 30  | ps   |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter from Y/Z(2:4) residual jitter                       | Am/Bm = 1.65 Gbps HDMI data pattern,<br>m = 2, 3, 4<br>A1/B1 = 165 MHz clock                               |     | 18                 | 50  | ps   |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter from Y/Z(1) residual jitter                         | See Figure 8, PRE = 0 V                                                                                    |     | 20                 | 22  | ps   |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter from Y/Z(2:4) residual jitter                       | Am/Bm = 2.25 Gbps HDMI data pattern,<br>m = 2, 3, 4<br>A1/B1 = 225 MHz clock                               |     | 38                 | 78  | ps   |

| t <sub>PRE</sub>     | De-emphasis duration                                                           | See Figure 4, PRE = $V_{CC}$<br>Am/Bm = 250 Mbps HDMI data pattern,<br>m = 2, 3, 4<br>A1/B1 = 25 MHz clock |     | 240 <sup>(4)</sup> |     | ps   |

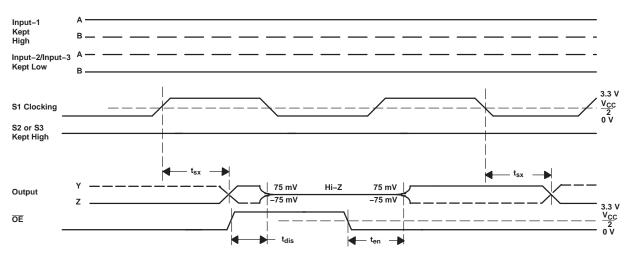

| t <sub>SX</sub>      | Select to switch output                                                        |                                                                                                            |     | 6                  | 10  | ns   |

| t <sub>en</sub>      | Enable time                                                                    | See Figure 6                                                                                               |     | 6                  | 10  | ns   |

| t <sub>dis</sub>     | Disable time                                                                   |                                                                                                            |     | 6                  | 10  | ns   |

| DDC I/O              | PINS (SCL, SCL_SINK, SDA, SDA_SINK)                                            |                                                                                                            |     |                    |     |      |

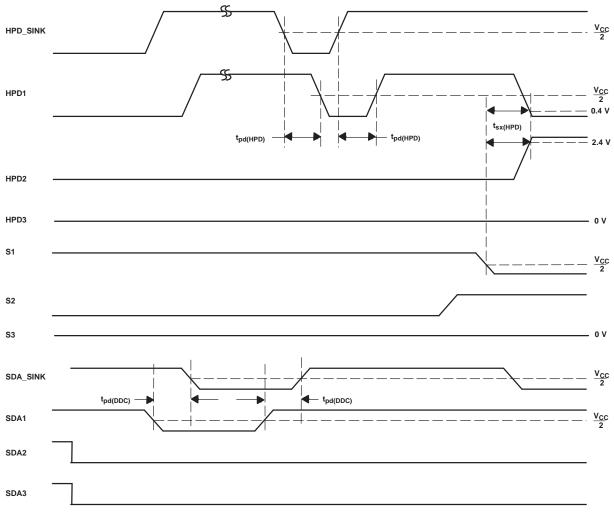

| t <sub>pd(DDC)</sub> | Propagation delay from SCLn to SCL_SINK or SDAn to SDA_SINK or SDA_SINK to SDA | See Figure 7, $C_L$ = 10 pF                                                                                |     | 0.4                | 2.5 | ns   |

| CONTR                | OL AND STATUS PINS (S, HPD_SINK, HPD)                                          |                                                                                                            |     |                    |     |      |

| t <sub>pd(HPD)</sub> | Propagation delay (from HPD_SINK to the active port of HPD)                    |                                                                                                            |     | 2                  | 6.0 | ns   |

| t <sub>sx(HPD)</sub> | Switch time (from port select to the latest valid status of HPD)               | See Figure 7, C <sub>L</sub> = 10 pF                                                                       |     | 3                  | 6.5 | ns   |

(1) All typical values are at 25°C and with a 3.3-V supply.

(2) t<sub>sk(o)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of channel 2 to 4 of a device when inputs are tied together.

(3) t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of channel 2 to 4 of two devices, or between channel 1 of two devices, when both devices operate with the same source, the same supply voltages, at the same temperature, and have identical packages and test circuits.

(4) The typical value is ensured by simulation.

#### PARAMETER MEASUREMENT INFORMATION

Figure 1. Termination for TMDS Output Driver

NOTE: All input pulses are supplied by a generator having the following characteristics: t<sub>r</sub> or t<sub>f</sub> < 100 ps, 100 MHz from Agilent 81250. C<sub>L</sub> includes instrumentation and fixture capacitance within 0.06 m of the D.U.T. Measurement equipment provides a bandwidth of 20 GHz minimum.

## PARAMETER MEASUREMENT INFORMATION (continued)

Figure 3. Short Circuit Output Current Test Circuit

## Figure 4. De-Emphasis Output Voltage Waveforms and Duration Measurement Definitions

Figure 5. Definition of Intra-Pair Differential Skew

Figure 6. TMDS Outputs Control Timing Definitions

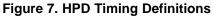

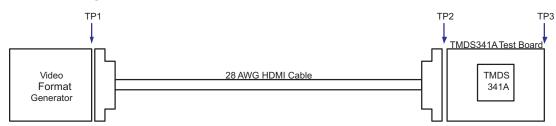

- A. All jitters are measured in BER of 10<sup>-12</sup>

- B. The residual jitter reflects the total jitter measured at the TMDS341A output, TP3, subtract the total jitter from the signal generator, TP1

#### Figure 8. Jitter Test Circuit

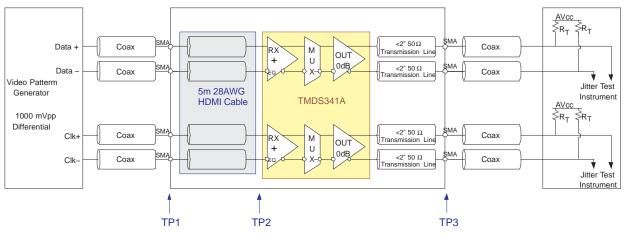

Figure 9 shows the frequency loss response from a 5m 28AWG HDMI cable and a 5m 28AWG DVI cable. The TMDS341A built-in passive input equalizer compensates for ISI. For an 8-dB loss HDMI cable, the TMDS341A typically reduces jitter by 60 ps from the device input to the device output.

#### TMDS341 input equalization gain vs. 5m DVI/HDMI cable response

Figure 9. S-Parameter Plots of 5-m DVI and HDMI Cables

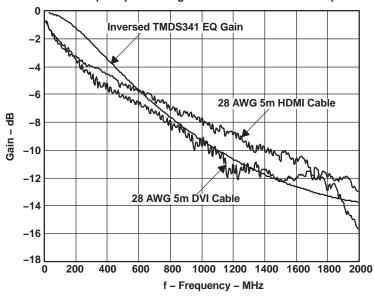

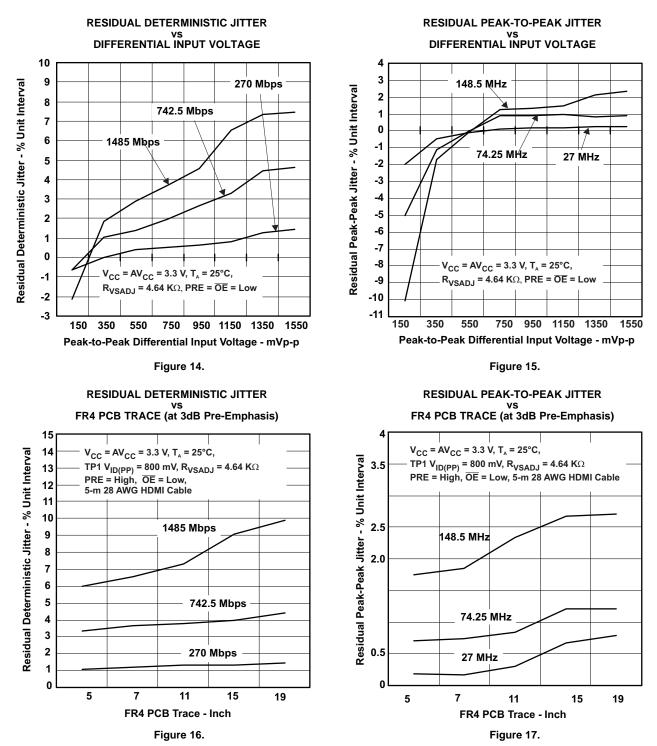

## **TYPICAL CHARACTERISTICS**

## **TYPICAL CHARACTERISTICS (continued)**

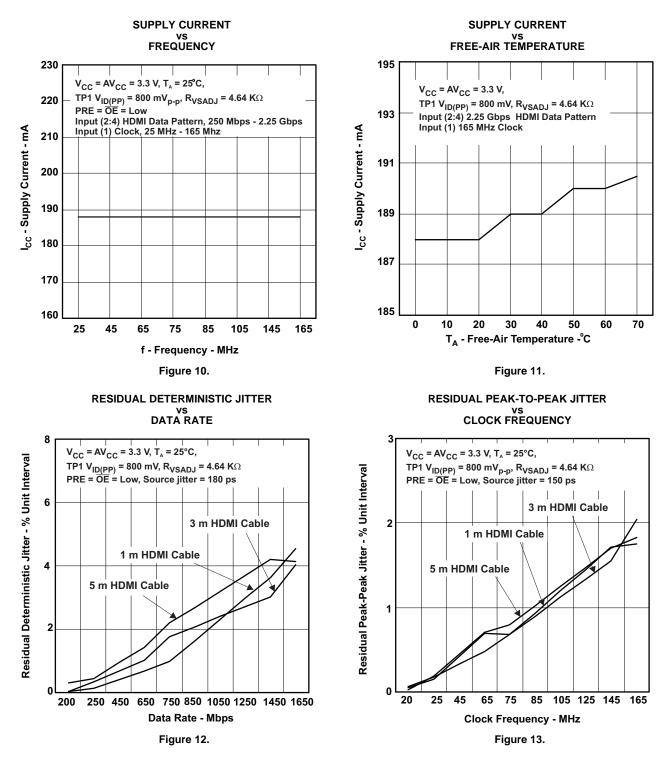

#### **TYPICAL CHARACTERISTICS (continued)**

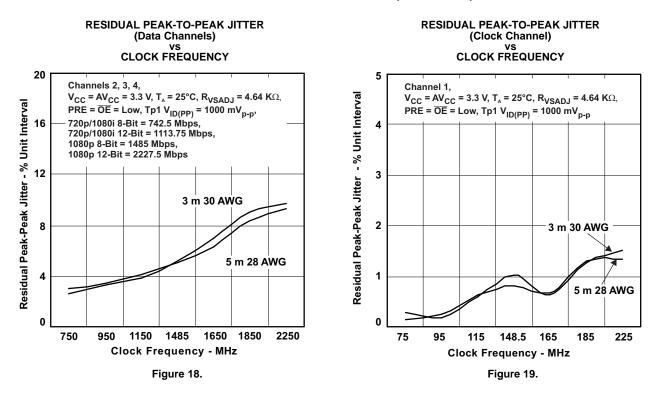

## **TYPICAL CHARACTERISTICS (continued)**

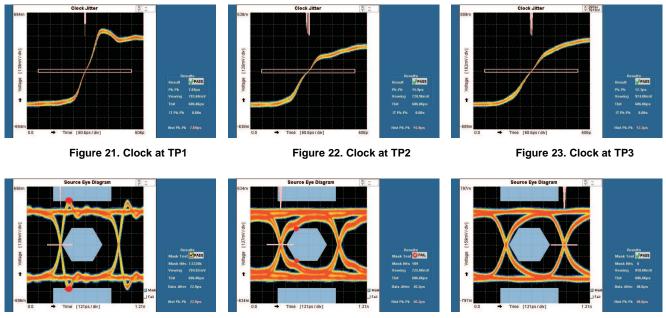

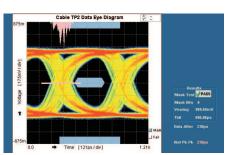

## HDMI Cables Running at 165-MHz Pixel Clock

Figure 20. 1-m and 5-m HDMI Cable Test Point Configuration

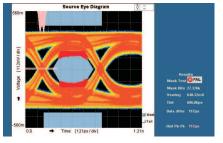

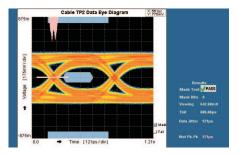

## 1-m Cable Length Eye Patterns

Figure 24. Data at TP1

Figure 25. Data at TP2

Figure 26. Data at TP3

## **TYPICAL CHARACTERISTICS (continued)**

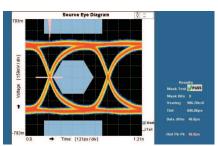

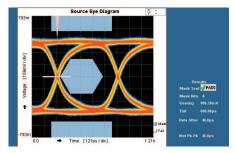

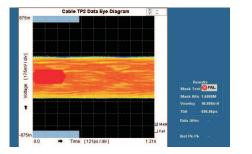

#### 5-m Cable Length Eye Patterns

Figure 27. Clock at TP1

0.00-

Figure 28. Clock at TP2

Figure 29. Clock at TP3

Figure 30. Data at TP1

Figure 31. Data at TP2

Figure 32. Data at TP3 (DC-Coupled Input)

Figure 33. Data at TP3 (AC-Coupled Input)

## **APPLICATION INFORMATION**

#### **Supply Voltage**

All  $V_{CC}$  pins can be tied to a single 3.3-V power source. A 0.01- $\mu$ F capacitor is connected from each  $V_{CC}$  pin directly to ground to filter supply noise.

## **TMDS** Inputs

Standard TMDS terminations are integrated on all TMDS inputs. External terminations are not required. Each input channel contains an 8-dB equalization circuit to compensate for cable losses. The voltage at the TMDS input pins must be limited per the absolute maximum ratings. An unused input should not be connected to ground as this would result in excessive current flow damaging the device.

#### TMDS Input Fail-Safe

TMDS input pins do not incorporate fail-safe circuits. An unused input channel can be externally biased to prevent output oscillation. One pin can be left open with the other grounded through a  $1-k\Omega$  resistor as shown in Figure 34.

Figure 34. TMDS Input Fail-Safe Recommendation

#### TMDS Outputs

A 1% precision resister, 4.64-k $\Omega$ , connected from VSADJ to ground is recommended to allow the differential output swing to comply with TMDS signal levels. The differential output driver provides a typical 10-mA current sink capability, which provides a typical 500-mV voltage drop across a 50- $\Omega$  termination resistor.

Figure 35. TMDS Driver and Termination Circuit

As shown in Figure 35, if  $V_{CC}$  (TMDS341A supply) and  $AV_{CC}$  (sink termination supply) are powered, the TMDS output signals are high impedance when  $\overline{OE}$  is high. Normal operation is with both supplies active.

Also shown in Figure 35, if  $V_{CC}$  is on and  $AV_{CC}$  is off, the TMDS outputs source a typical 5-mA current through each termination resistor to ground. The terminations consume a total of 10 mW of power independent of the  $\overline{OE}$  logical selection. When  $AV_{CC}$  is powered on, normal operation ( $\overline{OE}$  controls output impedance) is resumed.

#### **APPLICATION INFORMATION (continued)**

When the power source of the device,  $V_{CC}$ , is off and the power source to termination,  $AV_{CC}$ , is on, the output leakage current ( $I_{o(off)}$ ) specification ensures leakage current is limited to 10-µA or less.

The PRE pin provides 3-dB de-emphasis, allowing output signal pre-conditioning to offset interconnect losses from the TMDS341A outputs to a TMDS receiver. PRE is recommended to be low to the circuit design of a stand-alone switch box.

#### **HPD Pins**

The input of the HPD\_SINK is 5-V tolerant, allowing direct connection to 5-V signals. The HPD pin output resistance is  $35-\Omega$  typically. A 1-k $\Omega$  10% resistor is recommended to be connected from an HPD pin at the TMDS341A to the HPD pin of the HDMI connector.

#### DDC Channels

The DDC channels are designed with a bi-directional pass gate, providing 5-V signal tolerance. The 5-V tolerance allows direct connection to a standard  $I^2C$  bus. The level shifter between 3.3 V and 5 V  $I^2C$  interface can be eliminated.

#### Configuring the TMDS341A as a 2:1 Switch

The TMDS341A can be configured as a 2-to-1 switch by pulling the source selector pin (S1, S2, S3) of the non-active port low and leaving the corresponding TMDS inputs, SCL, SDA, and HPD pins open.

#### Layout Considerations

The high-speed TMDS inputs are the most critical paths for the TMDS341A. There are several considerations to minimize discontinuities on these transmission lines between the connectors and the device:

- Maintain  $100-\Omega$  differential transmission line impedance into and out of the TMDS341A

- Keep an uninterrupted ground plane beneath the high-speed I/Os

- Keep the ground-path vias to the device as close as possible to allow the shortest return current path

- Layout of the TMDS differential inputs should be with the shortest stubs from the connectors

#### **Connecting Cables Longer Than 5 m**

When using the TMDS341A with cables longer than 5 m, the impact to the TMDS signal path as well as the DDC signal path must be considered.

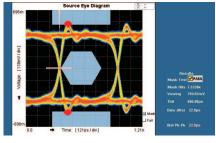

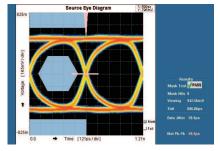

#### **TMDS Signal Path**

The TMDS341A receiver equalization circuit provides the capability of compensating inter-symbol interference (ISI) losses in a 5-m 28-AWG DVI cable. Typical cable measurements indicate that the TMDS341A can drive a 5-m 28-AWG HDMI cable and pass the eye mask at the output of a HDMI source (TP1) and a 10-m 28-AWG HDMI cable and pass the eye mask at the input of a HDMI sink (TP2). Figure 36 through Figure 39 show the eye mask measurement results.

Figure 36. Eye Diagram at Output 5-m 28-AWG Cable vs TP1 Eye Mask

Figure 37. Eye Diagram Recovered by TMDS341A vs TP1 Eye Mask

## **APPLICATION INFORMATION (continued)**

Figure 38. Eye Diagram at Output 10-m 28-AWG Cable vs TP2 Eye Mask

Figure 39. Eye Diagram Recovered by TMDS341A vs TP2 Eye Mask

#### **DDC Signal Path**

Observed I<sup>2</sup>C bus voltage is dependent on bus resistance, capacitance, and time. The transient bus voltage, when charging from a low state to a high state, can be calculated using equation (1).

$$V(t) = V_{DD}(1 - e^{-t/RC})$$

Where:

t is the time since the charging started

$V_{\text{DD}}$  is the pull-up termination voltage

R is the total resistance on the I<sup>2</sup>C link

C is the total capacitance on the  $I^2C$  link

In the I<sup>2</sup>C bus specification, version 2.1, the high-level threshold voltage is  $V_{IH} = 0.7 V_{DD}$ , and the low-level threshold voltage is  $V_{IL} = 0.3 V_{DD}$ .

From equation (1), the times to charge from a bus voltage of 0 V to the  $V_{IH}$  and  $V_{IL}$  levels are:

$t_{\rm IH} = 1.204 \times \rm RC$  $t_{\rm IL} = 0.357 \times \rm RC$

The bus rise time (from 0.3  $V_{DD}$  to 0.7  $V_{DD}$ ) is then given by equation (2):

$t_{r(30-70)} = t_{IH} - t_{IL} = 0.847 \times RC$

(2)

(1)

The TMDS341A can be easily applied in stand-alone switch boxes and digital displays. The following sections show the bus lengths that can be supported in each case.

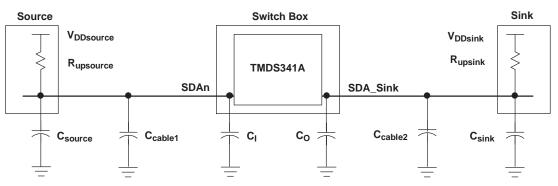

#### Maximum Bus Lengths for Switch Applications

Figure 40 shows the TMDS341A being used as a stand-alone switch. Both pull-up resistors are decided by the source and sink equipment. A 1.5-k $\Omega$  resistor at the source and a 47-k $\Omega$  resistor at the sink are recommended.

## **APPLICATION INFORMATION (continued)**

Figure 40. DDC Link from Source to Sink With External Switch Box

$R_{upsource} = 1.5$ -k $\Omega$  pull-up to 5 V

$R_{upsink} = 47$ -k $\Omega$  pull-up to 5 V

$R_{total} = R_{upsource} // R_{upsink} = 1.45 \ k\Omega$

$C_{total} = C_{source} \ // \ C_{cable1} \ // \ C_i \ // \ C_o \ // \ C_{cable2} \ // \ C_{sink}$

For standard mode I<sup>2</sup>C, the frequency is at 100 kHz, and the transition time must be less than 1  $\mu$ s. The total allowable capacitance, C<sub>total</sub>, is then 814-pF. C<sub>source</sub> and C<sub>sink</sub> are limited by the HDMI specification to 50 pF. C<sub>i/o</sub> for the TMDS341A is 10 pF max. The total capacitance from DVI or HDMI cables, C<sub>cable1</sub> and C<sub>cable2</sub>, should then be less than 704 pF.

Typical capacitance is 200 pF for a 28-AWG 5-m HDMI cable and 300 pF for a 28-AWG 5-m DVI cable. The recommended total cable length is the length of cable 1, Lcable1, plus the length of cable 2, Lcable2. For a 28-AWG DVI cable, the total cable length is 11 m; and for a 28-AWG HDMI cable, the total cable length is 17 m.

This calculation is applicable to  $V_{IH} \leq V_{pass}$ .

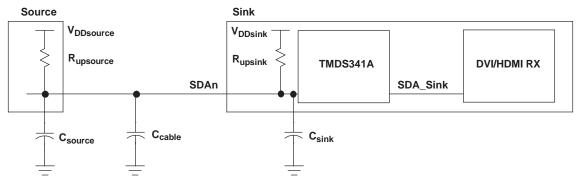

#### Maximum Bus Lengths for DTV Applications

Figure 41 shows the TMDS341A being used as a switch in a DTV and being placed on the same PCB board as the DVI/HDMI receiver. Unlike Figure 40, the output connector of the TMDS341A stand-alone switch and the input connector of the sink are removed, which results in a lower capacitance in the DDC link and eliminates the impedance discontinuity. However, the capacitance of the removed connectors is relatively small, relative to the total allowable capacitance. The results from the previous section *Maximum Bus Lengths for Switch Applications* can be reused if the pull-up resistors and capacitances have the same values. The recommended total cable length is the length from source to sink.

## **APPLICATION INFORMATION (continued)**

Table 2 summarizes the recommended cable lengths based on threshold voltages V\_{IH} = 0.7 V\_{DD} and V\_{IL} = 0.3 V\_{DD}.

# Table 2. Recommended Cable Lengths Under General Threshold Voltages, 0.7 $V_{\text{DD}}$ and 0.3 $V_{\text{DD}}$ , of a DDC Interface

| DDC THRESHOLD VOLTAGE, V <sub>IH</sub> = 0.7                           | $V_{DD}, V_{IL} = 0.3 V_{DD}$ | TOTAL CABLE LENGTH (m)       |                        |  |  |

|------------------------------------------------------------------------|-------------------------------|------------------------------|------------------------|--|--|

| SUGGESTED PULL-UP RESISTANCE (k $\Omega$ )                             | CABLE TYPE                    | SWITCH BOX Lcable1 + Lcable2 | DIGITAL DISPLAY Lcable |  |  |

| $R_{upsource} = 1.5 \text{ k}\Omega$                                   | 28-AWG DVI                    | 11                           | 11                     |  |  |

| $R_{upsource} = 1.5 \text{ k}\Omega$ $R_{upsink} = 47 \text{ k}\Omega$ | 28-AWG HDMI                   | 17                           | 17                     |  |  |

Applying the same methodology to the case of  $V_{IH} = 1.9$  V and  $V_{IL} = 0.7$  V, Table 3 summarizes the recommended cable lengths to meet the timing requirement of the DDC interface.

# Table 3. Recommended Cable Lengths Under General Threshold Voltages, 1.9 V and 0.7 V, of a DDC Interface

| DDC THRESHOLD VOLTAGE, V <sub>IH</sub> = 1.                            | 9 V, V <sub>IL</sub> = 0.7 V | TOTAL CABLE LENGTH (m)       |                        |  |

|------------------------------------------------------------------------|------------------------------|------------------------------|------------------------|--|

| SUGGESTED PULL-UP RESISTANCE (kΩ) CABLE                                |                              | SWITCH BOX Lcable1 + Lcable2 | DIGITAL DISPLAY Lcable |  |

| $R_{\mu\nu\rho\sigma} = 1.5 \text{ k}\Omega$                           | 28-AWG DVI                   | 16                           | 16                     |  |

| $R_{upsource} = 1.5 \text{ k}\Omega$ $R_{upsink} = 47 \text{ k}\Omega$ | 28-AWG HDMI                  | 24                           | 24                     |  |

## **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | hanges from A Revision (November 2006) to B Revision                                    | Page |

|----|-----------------------------------------------------------------------------------------|------|

| •  | Changed signaling rate from 1.65 Gbps to 2.25 Gbps and color depth from 8-bit to 12-bit | 1    |

| •  | Changed 1.65 Gbps to 2.25 Gbps                                                          | 1    |

| •  | Changed from 1.65 Gbps to 2.25 Gbps                                                     | 7    |

| •  | Added data channels residual peak-to-peak jitter curves                                 | 16   |

|    | Added clock channel residual peak-to-peak jitter curves                                 |      |

| •  | Added A to the device on test board                                                     | 17   |

## PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| TMDS341APFC      | ACTIVE                | TQFP            | PFC                | 80   | 96             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| TMDS341APFCG4    | ACTIVE                | TQFP            | PFC                | 80   | 96             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| TMDS341APFCR     | ACTIVE                | TQFP            | PFC                | 80   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| TMDS341APFCRG4   | ACTIVE                | TQFP            | PFC                | 80   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

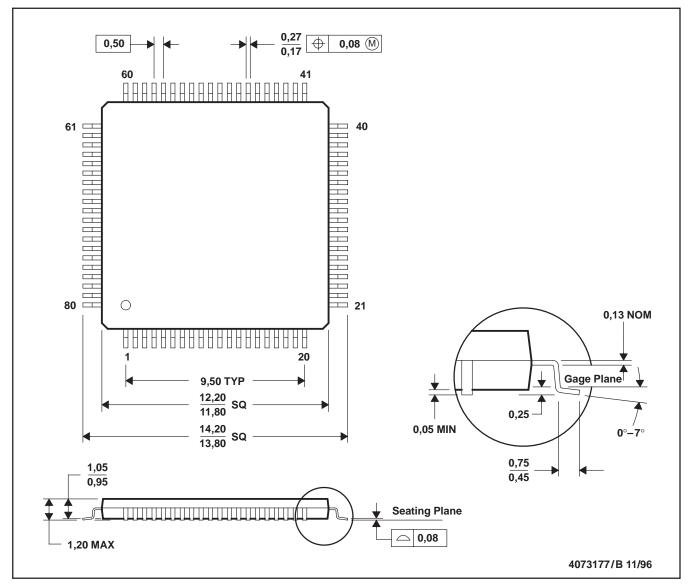

## **MECHANICAL DATA**

MTQF009A - OCTOBER 1994 - REVISED DECEMBER 1996

#### PFC (S-PQFP-G80)

PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-026

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DLP® Products               | www.dlp.com            | Broadband          | www.ti.com/broadband      |

| DSP                         | dsp.ti.com             | Digital Control    | www.ti.com/digitalcontrol |

| Clocks and Timers           | www.ti.com/clocks      | Medical            | www.ti.com/medical        |

| Interface                   | interface.ti.com       | Military           | www.ti.com/military       |

| Logic                       | logic.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Power Mgmt                  | power.ti.com           | Security           | www.ti.com/security       |

| Microcontrollers            | microcontroller.ti.com | Telephony          | www.ti.com/telephony      |

| RFID                        | www.ti-rfid.com        | Video & Imaging    | www.ti.com/video          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Texas Instruments: TMDS341APFC TMDS341APFCG4 TMDS341APFCR TMDS341APFCRG4